基于Verilog实现电器定时开关控制

1、前言

随着当今社会工作和生活节奏的加快,人们对许多电器、仪器、设备的自动化要求也越来越高,但现有的许多电器还不具备定时开启和关闭功能,许多需要在固定时间开关的装置,还需人工值守和操作,因此设计带有时钟显示功能的多个电器定时开关控制系统,具有实际意义。

2系统功能及操作

系统上电时复位,时钟显示为0时0分0秒,按下"时间"设置键设定时间,数字钟开始工作,数码管显示当前时间;按下"开启电器编号"设置键,再按下要定时开启的电器编号,对应发光二极管亮,表示设置有效;按下"电器开启时间"设置按键;再依次输入4位十进制的小时和分钟,作为开启时间;按下"电器关闭时间"设置按键,再依次输入4位十进制的小时和分钟,作为关闭时间。至此定时开关设置完成,对于电饭锅等具有保持功能的电器,则不用设置定时关闭。使用Verilog HDL编写CPLD程序,理论上可同时设置多个电器的定时自动开启,本设计可同时设置3个电器。

3硬件设计

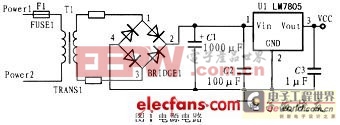

硬件设计采用Altera公司的CPLD EPM7128SLC84-6,简化了外围电路,稳定性和可靠性高,成本低。220 V、50 Hz工频电源经变压器、电桥整流后通过三端稳压器,提供工作电压,其电源电路如图1所示。

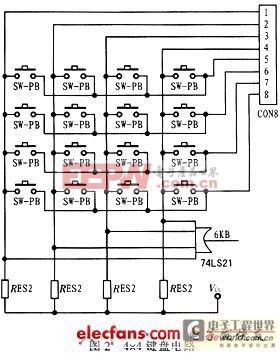

外接4×4键盘,使用较少的I/O端口线就可实现对较多按键的控制。当有键按下时,kb为低电平,CPLD的按键扫描部分采用动态扫描方式进行识别。设置14个按键,分别为0~9十个数字键和设定时间、开启电器编号、电器开启时间、电器关闭时间4个功能键,其余两个留作功能扩展。4×4键盘电路如图2所示。

本系统设计使用6个数码管显示时间,3个发光二极管标志是否定时。电器开启信号经三极管放大后接继电器,通过继电器吸合导通电源线,开启电器。

4软件设计

Verilog HDL是硬件设计人员和QuartusⅡ界面之间的交互手段,其具体物理建模能力强,设计方便,可读性好,语法类似C语言,与VHDL相比,更容易学习和掌握,与原理图设计法相比,设计和分析更容易,可避免考虑画面的布局及美观

评论