基于DM642DSP的视频编码优化方法

引言

当前在视频监控,视频会议,网络流媒体等方面数字视频编码成为最核心,最基本的技术手段,尤其是视频监控现已成为最为普通的安保设备之一。基于电脑硬盘为存储体的数字DVR已日渐取代模拟DVR。数字DVR的最关键技术就是视频压缩技术,而视频压缩技术又含有两大选择。首先是视频压缩采用何种算法标准,当前视频算法的国际标准有MPEG2、MPEG4、H.264,H.264以其高压缩效率,在低码率下优良的图像质量成为目前视频监控系统中首选的压缩方式。

但任何事物都有其两面性,H.264编码的高效率,优质图像是用算法的复杂性来换取的。H.264编码器的复杂性是MPEG2的4-5倍。第二个选择是用什么芯片来实现,TI公司的TMS320DM642芯片,是一款专门用作媒体处理的高速DSP,其强大的图像处理能力为在监控系统中实时实现H.264编码提供了可能。为了降低成本,还必须充分运用DM642本身的资源,使一颗DM642能处理更多路的视频,这就是高效率优化的目的,本文首先对整个视频监控的硬件平台做了介绍,后结合DM642的结构特点,提出整个编码软件的框架的安排,对于占用系统资源最多的运动估计提出基于DSP的优化方法,最后以整数DCT为例,讨论了编写汇编代码的技巧。

硬件平台的介绍

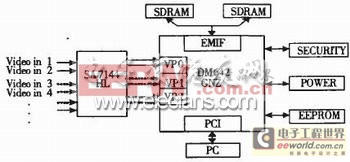

整个视频监控的硬件系统的框架如图1所示。DM642芯片为了适应数字媒体处理的需求,增加了三个可配置的视频端口(VP0,VP1,和VP2),这些视频口外设为常用的编解码设备提供了无缝接口。因而不需要外加可编程逻辑器件和FIFO就可满足系统设计的要求。

为了节省成本,提高DSP芯片的利用率,在一块板卡可以同时处理多路的音视频,压缩卡与主机间的数据吞吐量会很大,为了保证数据存储的实时性,系统采用PCI板卡,其与主机通信数据传输速率最高达528MB/s(66MHz,64bit),完全满足大容量高速实时传输系统的需求。

图1 硬件系统框架

由于每个视频口可以接收两路8/10bit的视频信号,视频信号经过SAA7144A/D转换输出为8位BT.656格式的数字视频数据。这样就能利用一颗DM642芯片处理最多6路视频输入。每个视频端口的BT.656视频采集模式采集8bit或是10bit4:2:2格式的亮度和色度信号,并将它们复用到一个数据流里,视频数据以Cb,Y,Cr,Y,Cb,Y,Cr的顺序传送,其中Cb,Y,Cr代表同一位置的亮度和色度样点,紧接着后面的Y代表下一个位置的亮度样点。数据流经解复用后亮度和色度信息分别存放到各自的Y,Cb,CrFIFO中,再经EDMA搬移到SDRAM中,以备CPU读取进行压缩编码。编码后的视频流再经PCI口存入到电脑的硬盘上,从而完成整个视频监控的流程。

编码器整体框架的安排

JM代码是很多可选的H.264标准软件之一,它关心H.264全部的功能在代码上得到体现,所有的情况都得考虑,例如帧编码,场编码都有,内存的分派没有考虑到系统的实际情况,适合用来帮助理解H.264标准,不太适合移植到DSP平台上。为了高效的组织利用DM642有限的片内资源,就得重新组织代码,包括数据结构,数据存放的位置,程序存放的位置,精简地来安排程序。

首先要考虑的是L2的配置问题,第二级L2(256kB)是一个统一的程序/数据空间,可以整体作为SRAM映射到存储空间,也可整体作为第二级cache,或者二者的比例的组合使用。因为一旦二级缓存也不命中的话,那么读取数据申请将转由EDMA来完成,CPU至少有13个cycle的延迟。所以我们总是尽量把程序和数据放在片内存储器内。但是即使全部将L2配置成SRAM也只有256kB大小,以CIF格式图像为例,待编码的一帧图像大小是148.5kB,再加上运动估计的参考图像就大大超过256kB了。所以在配置L2时,笔者选择的是SRAM224kB,L2cache32kB。首先考虑要放到SRAM的是表格,全局变量,栈数据和一些调用频繁的核心程序,如运动搜索,DCT变换,量化……而整个待编码图像和参考图像就只能放在片外存储空间了。

既然图像数据被存放到了片外存储空间中,就要涉及到数据在片内存储跟片外存储间的数据搬移,这可交由DM642强大的EDMA引擎来完成,EDMA工作时不占用CPU的周期,把CPU从繁重的搬移数据的工作中解放出来,专致于运算工作。在编码程序时,为了避免CPU等待EDMA搬完数据后才能工作,可采用乒乓结构的双缓存区,当EDMA传送数据到其中一块存储区域时,CPU对另一块存储区域进行处理。待二者都处理完

评论