石英晶体振荡线路误差来源及其回路分析

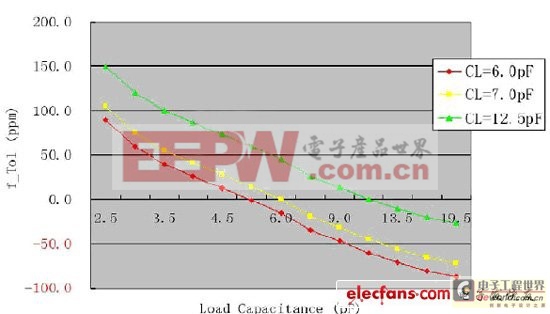

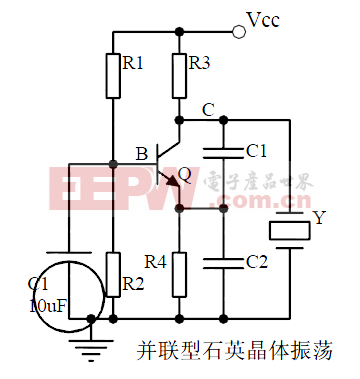

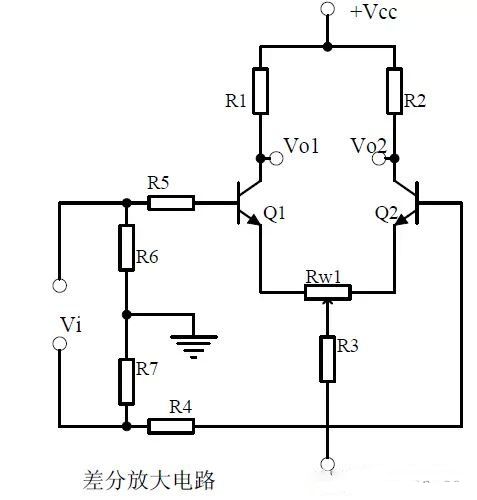

负载电容与频率容许误差的关系图:电容变大,频率变慢;电容变小,频率变快

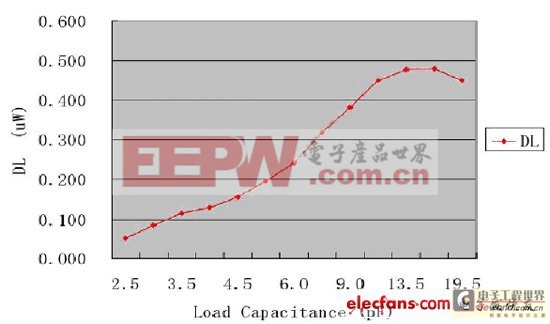

负载电容与驱动功率的关系图:当负载电容变小时,驱动功率也会变小

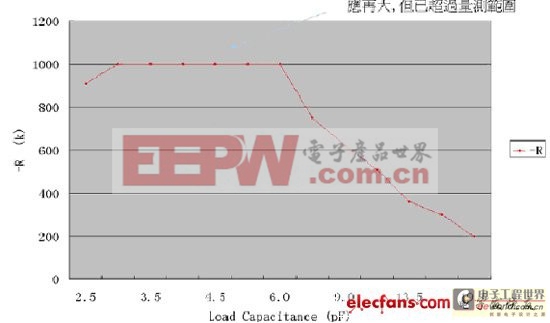

负载电容与负性阻抗的关系图:当负载电容变小时,负性阻抗会变大

[案例分析]

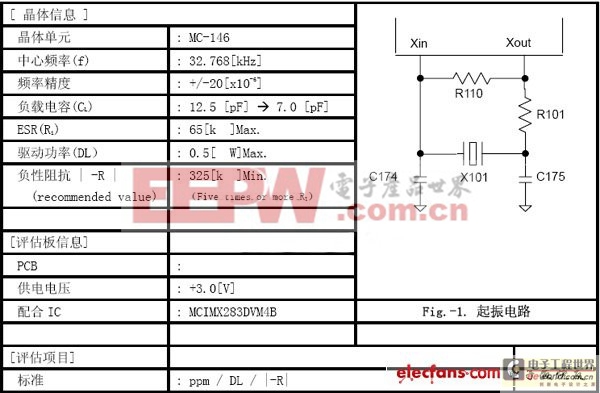

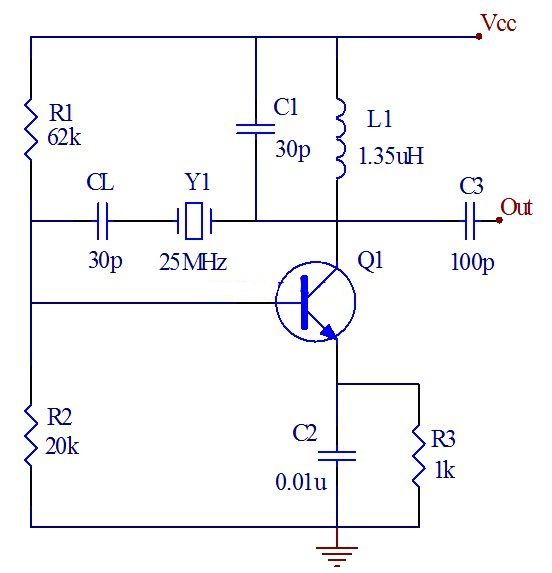

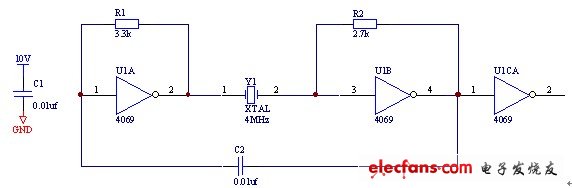

客户在应用MC-146的过程中发现会有10%左右的晶体起振时间过长、甚至不起振的现象发生。需要对电路设计进行测试来找到问题的原因和解决方法。

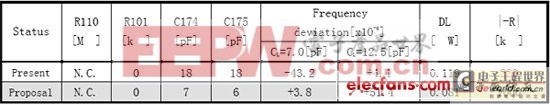

根据客户提供参数测试得到如下数据:

从测试结果看客户初始选择Cl=12.5pF的MC-146进行设计,匹配电容C174=C175=18Pf, 测得精度为+4.4 ppm满足应用要求。同时DL= 0.119W也小于0.5 W的要求。但是我们看到–R值为220 k不满足–R》5* ESR的要求。 该设计存在起振缓慢或停振的风险,因此需要对回路的器件参数进行重新设定。

重新设定的原则是:使振荡回路得到的参数指标都满足设计要求。

经过测试发现 Cl=12.5pF 的MC-146 在该系统的所有情况下都不能满足全部的参数要求,因此需要更换晶体单元。

结果显示当使用Cl=7 pF 的MC-146 的时候,匹配电容C174=7pF C175=6 pF, 测得精度为+3.8 ppm 满足应用要求。同时 DL= 0.081?W 也小于0.5W的要求。-R值为1000 k远远大 5倍ESR(325 k)。因此推荐客户使用该参数匹配的电路设计,可以保证得到稳定可靠的时钟频率。

评论