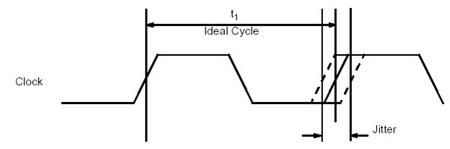

时域时钟抖动分析(上)二

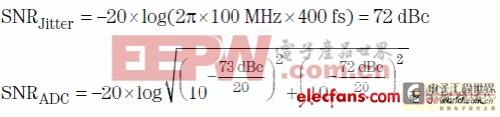

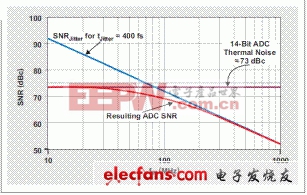

现在,很明显,如果 ADC 的热噪声增加,对高输入频率采样时时钟抖动便非常重要。例如,一个 16 位 ADC 具有 ~77 到 80 dB 的热噪声层。根据图 4 所示曲线图,为了最小化 100MHz 输入频率 SNR 的时钟抖动影响,时钟抖动需为大约 150 fs 或更高。

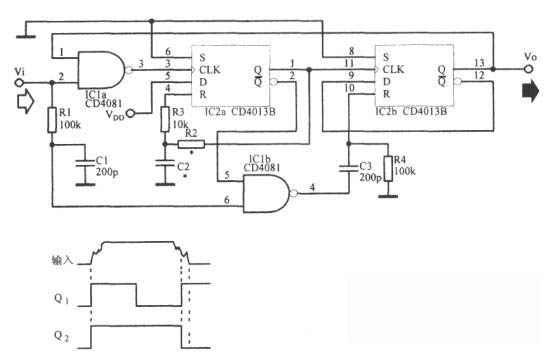

确定采样时钟抖动

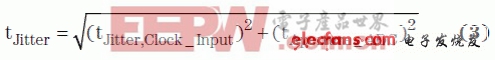

如前所述,采样时钟抖动由时钟的计时不准(相位噪声)和 ADC 的窗口抖动组成。这两个部分结合组成如下:

我们在产品说明书中可以找到 ADC 的孔径口抖动 (aperture jitter)。这一值一般与时钟振幅或转换速率一起指定,记住这一点很重要。低时钟振幅带来低转换速率,从而增加窗口抖动。

时钟输入抖动

时钟链(振荡器、时钟缓冲器或 PLL)中器件的输出抖动一般规定在某个频率范围内,该频率通常偏离于基本时钟频率 10 kHz 到 20 MHz(单位也可以是微微秒或者绘制成相位噪声图),可以将其整合到一起获取抖动信息。但是,低端的 10kHz 和高端的 20MHz 有时并非正确的使用边界,因为它们调试依赖于其他系统参数,我们将在后面进行详细介绍。图 6 描述了设置正确整合限制的重要性,图中的相位噪声图以其每十倍频抖动内容覆盖。我们可以看到,如果将下限设定为 100-Hz 或 10kHz 偏移,则产生的抖动便极为不同。同样地,例如,设置上整合限制为 10 或 20MHz,可得到相比 100MHz 设置极为不同的结果。

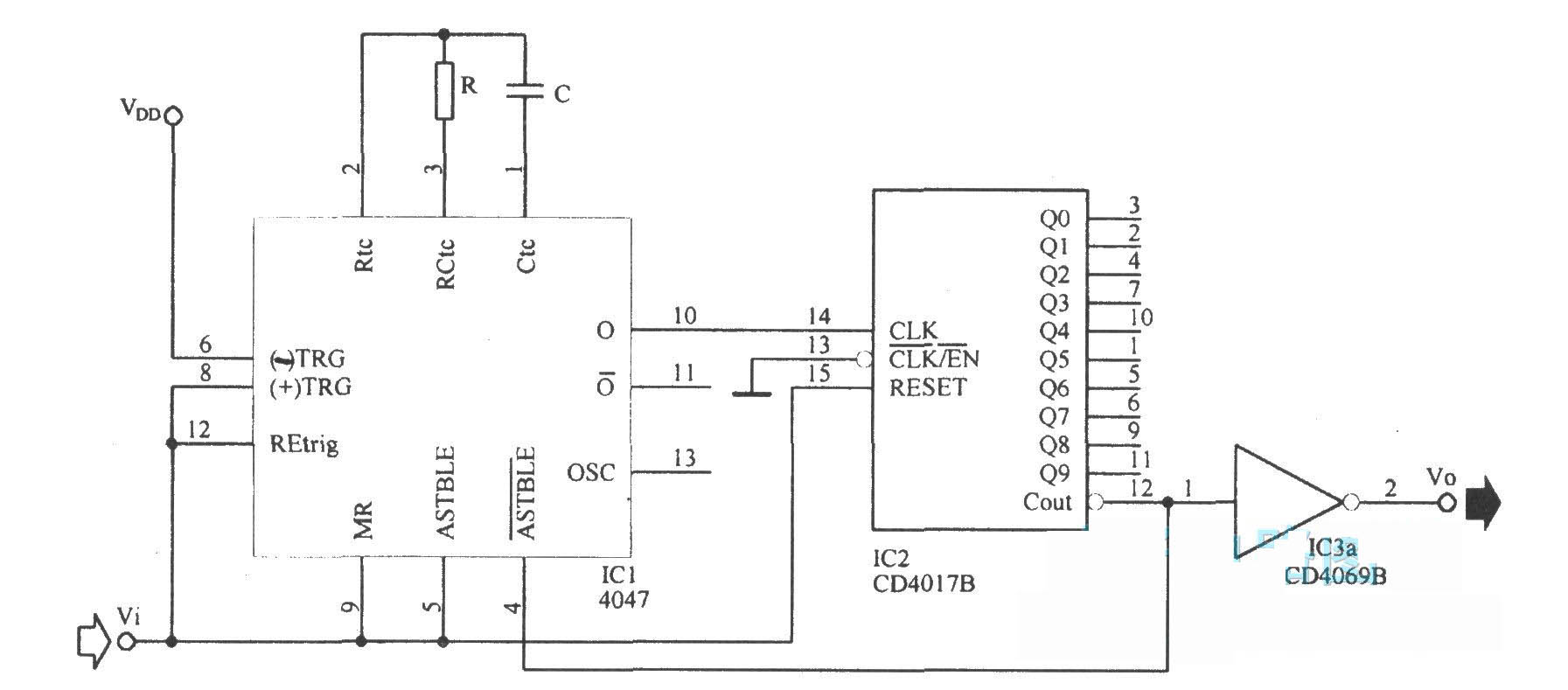

图 5 产生的 ADC SNR 受热噪声和时钟抖动的限制

评论