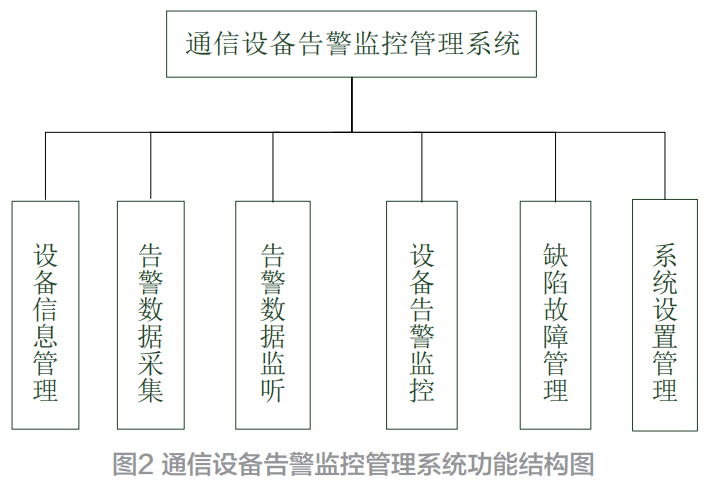

基于SOPC的数据采集与处理系统设计

SOPC技术将CPU、存储器、I/O接口等系统设计所必须的模块集成在一片FPGA上,是一种新的系统设计技术。这种设计方式,具有开发周期短、设计灵活、可裁减、可扩充、可升级、软硬件在系统可编程的功能,特别适用于复杂系统的设计。

本文给出了一种基于SOPC的数据采集与处理系统的设计方案。系统用24位模数转换芯片实现多通道地震数据前端采集;利用FPGA的可并行及高速运算特点,用FPGA代替传统的DSP芯片,设计并行的数据信号同步处理,以提高系统的实时性和同步性。该系统成功地应用到矿井地震勘探中,得到良好的效果。

1 系统硬件实现

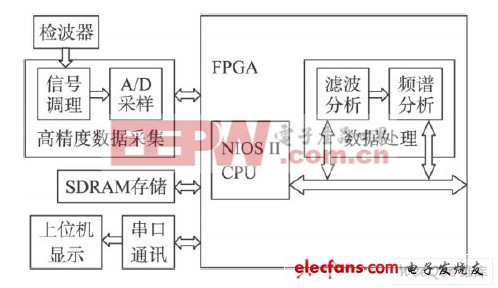

数据采集与处理系统主要是对数据的采集以及对得到数据的处理,本系统采用SOPC技术,以软核处理器N IOS II为控制核心,N IOSⅡCPU和各IP模块之间通过Avalon片上总线相连。系统原理图见图1所示。系统主要由四个硬件模块构成:数据采集模块、数据处理模块、数据存储模块和数据通讯模块。数据采集模块主要用24位高精度A /D芯片进行地震数据采集; 数据处理模块主要用FPGA实现各DSP算法; 数据存储模块采用SDRAM实现;数据通讯模块采用RS232串口通讯,负责把数据上传到上位机上显示。

图1 系统原理图

1. 1 NIOS II CPU

Nios II系列软核处理器是Altera的第二代FP2GA嵌入式处理器,是一个用户可配置的通用Risc嵌入式处理器,扩展了目前世界上最流行的软核嵌入式处理器的性能。用户可以从三种处理器(快速、标准、经济)以及超过60个的IP核中选择所需要的,NiosII系统为用户提供了最基本的多功能性,设计师可以以此来创建一个最适合他们需求的嵌入式系统。本设计采用的是标准型的N IOS IICPU,并调用了SDRAM 控制器和异步串口URAT (RS_232 Serial port)等接口IP。

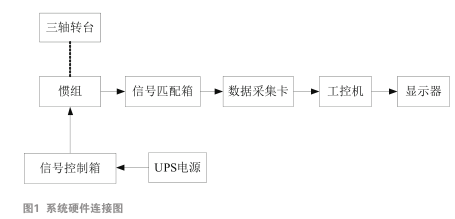

1. 2 数据采集模块

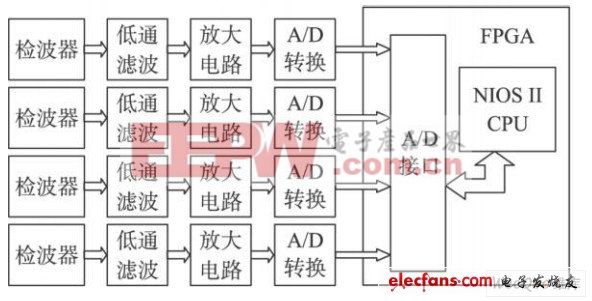

数据采集模块采用多通道同步采集,其基本原理如图2所示: 4通道同步采集,每个通道由信号前端调理电路、模数转换采样电路及A /D接口构成。

对采集信号的调理,主要是针对信号的滤波和信号放大处理:地震检波器采集来相关数据后,使用无源低通滤波器去除高频无用信号,以防止后续数字滤波产生频谱混叠;使用高速反馈放大器OPA1632D实现对输入模拟数据的放大。对于采样电路,使用24位的A /D7766芯片,该芯片在以125 kHz输出数据速率工作时具有108 dB的动态范围,它比具有相同输出数据速率的同类器件高3 dB,其特别适合地震采集的低功耗和鉴别大信号中的微弱信号要求。

图2 数据采集模块原理图

1. 3 数据处理模块

SOC系统的一个重要思想就是IP复用,因此本文充分利用了ALTERA公司丰富的DSP IP核资源以提高产品开发效率,实现多通道数据的并行同步处理。

1. 3. 1 数字滤波模块

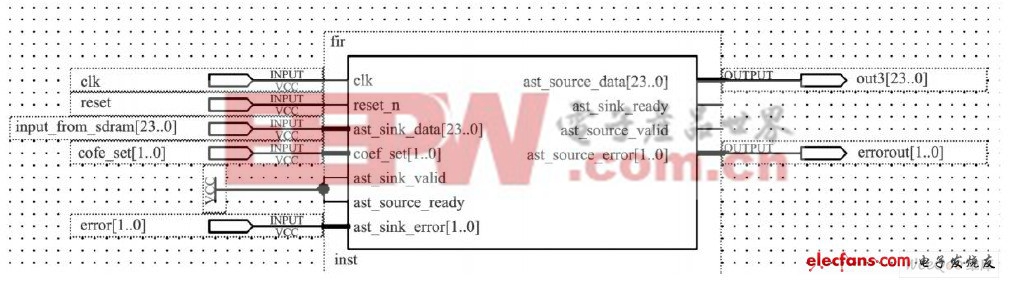

对于地震勘探来说,由检波器接收到的有效地震信号具备多频率特性。为了现场技术人员更好地了解地质情况,需要看到特定范围频带的信号,因此需要设计一个具备多频带的带通滤波器。滤波模块调用了Altera公司的F IR IP核来生成,通过设置参数,即可实现不同要求的滤波器。

本系统生成的滤波模块图如图3 所示,其中cofe_set为滤波选择信号,可以通过N IOS II提供给cofe_set值命令,完成四种不同带宽的通带滤波。

图3 滤波模块图

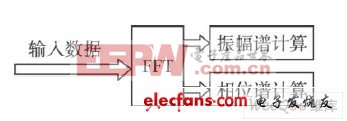

1. 3. 2 频谱分析模块

为了了解地震信号的频谱分布范围,需要对随时间变化的地震信号进行傅里叶变换,以得到随频率而变化的振幅和相位的函数。本设计的原理图如图4所示:先采用ALTERA公司的FFT IP核设计一个1 024点的FFT模块,得到的数据再送给相位谱计算模块和振幅谱计算模块得到振幅谱和相位谱。

图4 频谱分析模块原理图

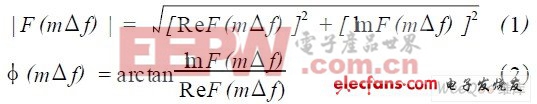

振幅谱、相位谱的公式见式( 1)与式( 2) , ReF(mΔf)和ImF (mΔf)为输入数据经FFT模块处理后得到的实部和虚部值。

由式(1)可知,振幅谱模块主要由乘法模块、加法模块及开方模块组成,其都可以用ALTERA公司对应的IP核来实现。对于相位谱模块,其需要求反正切函数,对此本设计用了基于查找表的设计方法。

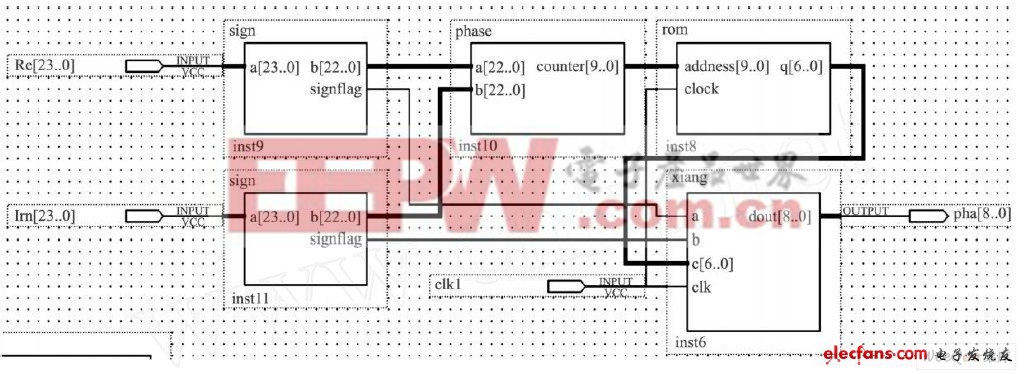

如图5所示:在phase中把实部Re的绝对值乘100后除以虚部Im的绝对值,得到的值按照一定的规律转化成Counter (从0到1 024) 。rom中事先存着0到90的相位值, Counter做为RAM的地址输入,此时通过Counter的值就可以查找出对应的相位。再根据sign产生的实部、虚部的符号来判断相位的象限,得出0到360°范围的相位值。

图5 相位谱模块电路图

1. 4 SDRAM外部存储

为了对数据进行缓存,本设计采用了hy57v561620SDRAM外部存储芯片。SDRAM具有大容量和高速度的特点,满足地震勘探的大数据容量和高速度要求。

在SOPC Builder中,已经存在基于Avalon 接口的SDRAM控制内核,用户可以很方便的使用SDRAM控制器创建一个可以灵活的与SDRAM芯片接口的储存系统。

模块工作在96 M的系统主时钟下,当接收到N IOS II发出的读命令后, SDRAM开始读取A /D传来的数据,直到数据存放完毕。然后在N IOS II的控制下,再与DSP模块进行互相间的数据传输。

1. 5 通讯模块

为了把数据上传到上位机上进行显示,本系统采用了RS232 串口通信,串口通信的概念非常简单,串口按位发送和接收字节,可以在使用一根线发送数据的同时用另一根线接收数据,此外它还能够实现远距离通信。在SOPC Builder中,也已经存在基于Avalon接口的UART内核接口,为Altera FPGA上的嵌入式系统和外部设备提供了串行字符流的通信方式,内核执行RS2232协议时序。

2 系统软件设计

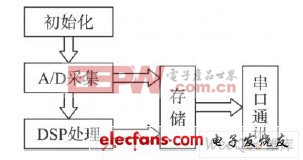

软件设计主要包括驱动程序和应用级代码编写等部分,如图6所示。在Nios II IDE中建立新的软件工程时, IDE会根据SOPC Builder对系统的硬件配置自动生成一个定制HAL (硬件抽象层)系统库。这个库能为程序和底层硬件的通信提供接口驱动程序,之后进行编译、调试、下载软件到开发板上。

图6 系统软件结构框图

本设计的应用程序流程如图7所示:系统工作时先初始化,接着控制A /D模块进行数据采集,采集来的数据进行直接送入DSP模块进行实时处理,并把处理前和处理后的数据都存储到SDRAM中。

最后把SDRAM中的数据经过串口发送到PC机上。

图7 应用程序流程图

3 系统实验结果

低通滤波器相关文章:低通滤波器原理

评论