一种基于DSP的视频监控系统解决方案

目前视频监控广泛应用于安防监控、工业监控和交通监控等领域。视频监控系统大致经历3个阶段:首先是基于模拟信号的电视监控系统,其功能单一、易受干扰且不易扩展;随后出现基于PC机的图像监控系统,其终端功能较强.但价格昂贵,稳定性差;近年来,随着嵌入式技术成熟,嵌入式视频采集处理系统具有可靠性高、速度快、成本低、体积小、功耗低、环境适应性强等优点。

基于嵌入式系统的上述诸多优点,这里提出一种基于DSP的视频监控系统解决方案。

2 系统硬件设计

2.1 系统整体硬件结构

整个系统硬件设计由电源、视频信号处理、FPGA和外围接口等模块组成。其中,图像处理模块接收CCD图像传感器传送的模拟视频信号,并把模拟视频信号模数转换成数字信号,由DSP处理所转换的数字信号,再转换为标准的YUV 4:2:2格式的数字视频信号,并将获得的数字视频信号送至FPGA模块,对YUV数字信号进行处理,从而产生标准的SVGA格式,帧频为60 Hz的行、场同步信号。图1为该系统硬件设计框图。

2.2 电源模块

电源模块将外部输入的12 V直流电源转换成系统各模块所需工作电压。CCD图像传感器所需电压为15 V和-7 V,DSP所需电压为3.3 V和5 V,FPGA所需电压为1.2 V、2.5 V和3.3 V。本设计采用MOTOROLA公司的DC-DC电源转换器,MC34063A将12 V直流电压转换成5 V直流电压,选用Texas Instruments公司的电源转换器TPS75003将5 V直压电源转换成1.2 V、2.5 V和3.3 V直流电压。而CCD图像传感器的工作电压则由NE555和78L15产生。

2. 3 图像处理模块

2.3.1 图像采集

本设计图像采集电路将CCD传感器输出的模拟视频信号转换成离散的模拟视频信号,再对模拟信号进行相关双采样、自动增益控制处理后,传输至DSP转换为数字信号。具体工作流程:系统上电复位后,DSP(CXD3142)产生控制信号驱动CCD图像传感器,把光信号转换成PAL制式的模拟视频信号,并把该信号输入到CXA2096N的引脚DIN和PIN引脚。此时,在引脚SHD和SHP的控制下对输入信号进行相关双采样。当SHD信号的下降沿到来时,采样DIN信号电平,当SHP信号的下降沿到来时,再采样PIN引脚的预加电平信号,将这两路信号送到CXA2096N内部的自动增益控制电路,经差运算后输出。再对输出信号进行黑电平箝位、预消隐等处理,然后由CXA2096N的DRVOUT引脚输出。DSP产生CXA2096N的工作时序。

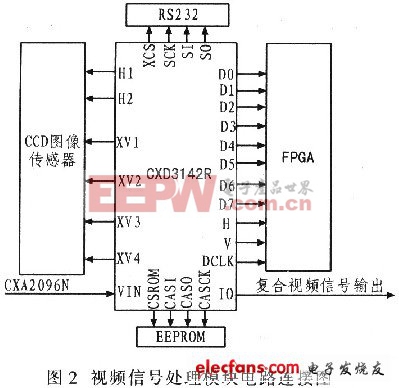

2.3.2 视频信号处理(CXD3142R)

本设计采用SONY公司专用信号处理器件CXD3142R作为信号处理器。CXD3142R是专用于对Ye,Cv,Mg和G补色单片CCD输出信号进行处理的低功耗、高效率的信号处理器;具有自动曝光和自动白平衡功能,可同时输出复合视频信号和YUV 8位数字信号输出。内部集成9位A/D转换器同步信号产生电路、外部同步电路和时钟控制电路。此外,CXD3142R还具有串口通信功能,用户可在PC机中预先设定好DSP中的寄存器值,通过串口下载到DSP,并对图像信号进行自动曝光和自动白平衡等处理。图2为视频信号处理模块电路连接图。

图2中,H1,H2,XVl,XV2,XV3,XV4是CCD图像传感器的时序驱动信号,EEPROM用来存储DSP初始化的寄存器值。D0~D7是YUV数字信号。其具体工作流程:将CCD图像传感器采集的模拟信号经CXA2096N进行相关预处理后,相应数字信号经VIN引脚传给DSP(CXD3142),DSP接收数字信号后,利用其内部AE/AWB检测电路、同步信号产生电路、外同步电路以及相关算法对其进行相关处理,处理完成后在行(H引脚)、场(V引脚)信号及时钟信号(PCLK)的控制下将8位数字信号经过D0~D7引脚传给FPGA模块进行相关处理。通过引脚SCK、SI、SO、XCS串口通信,通过CSROM、CASI、CSASO、CASCK引脚与外部EEPROM通信,实现DSP相关的初始化。此外,IO引脚输出经DSP处理过的复合视频信号,通过相关接口直接在CRT显示器上显示图像处理结果。

2.3.3 FPGA模块

为了实现实时预处理数字视频信号数据,增加系统扩展性,该系统设计扩展一片由Xilinx公司生产的基于90 nm工艺制造的Spartan3E系列FPGA,其型号为XC3S250E-PQ208-4C,此FPGA具有较高的性价比,其内有25万个系统门,5508个逻辑单元(LC),612个可配置逻辑块(CLB),216 Kbit的块RAM,12个专用乘法器,158个可用的I/O接口,4个数字时钟管理单元(DCM)。图3为其电路连接图。

DSP与FPGA的通信是由11根总线完成的,分别是8根数据线,行、场同步信号和数据时钟总线。因为CXD3142RDSP输出PAL(逐行倒相)制式的数字视频信号,FPGA将此PAL制视频信号转换成VGA格式。首先将YUV(4:2:2)格式信号转换成RGB(5:6:5)格式,然后利用2个SDRAM作为帧缓存,利用场间插值算法,完成隔行到逐行的转换,并将帧率由25 Hz提升到60 Hz,同时产生SVGA格式、帧频为60 Hz的行、场同步信号,并把被放大的图像数据经D/A转换后输出到VGA接口,VGA显示器上实时显示采集的图像。

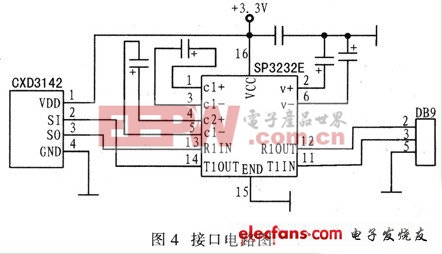

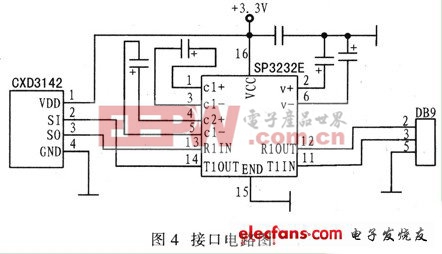

2.4 外围接口模块

本设计支持RS-232C串口通信。但该串口通信需把3.3 V逻辑电平转化成RS-232C标准电平。因此采用SP3232E系列器件完成电平转换。SP3232E可从+3.0~+5.5 V的电源电压产生2Vce的RS-232C电压电平。该系列适用于+3.3 V系统。SP3232E器件的驱动器满载时典型数据速率为235 kb/s。图4为系统设计的接口电路图。

需要注意的是,由于采用SP3232E器件,其驱动能力有限,该接口电路只适用于近距离传输。如果要进行远距离传输,则必须加强信号传输能力。

3 系统硬件调试

系统硬件调试应先调试电源模块,如果系统电源错误,器件将损坏;然后调试DSP模块。DSP上电后,空闲情况下一般不会发热,若有轻微的发热情况应立即断开电源以免损坏DSP器件,其主要原因是把DSP的工作电压接到DSP的非电压引脚。DSP的工作电压正常后,再检查复位电路、时钟电路是否正确。如果DSP的时钟引脚无信号,一般是电路虚焊。如果有信号,但工作频率达不到系统工作的正常值,则通过调整外部可调电容。如果还达不到要求,则应考虑时钟信号是否受到低频信号干扰,就要认真检查电路板,必要时应修改布线。FPGA模块的调试与上述方法相同。

4 结论

该系统设计已成功应用于数字视频展台项目。目前该产品已投入生产,但图像质量还有待提高,可能是模拟视频信号失真和白平衡的值设置不恰当。该设计方案具有较强的灵活性,还可应用于监控、安防等产品开发。

评论