CMOS集成电路设计(三):CMOS设计注意事项

①TTL集成电路的电源电压不能高于+5.5V使用,不能将电源与地颠倒错接,否则将会因为过大电流而造成器件损坏。

②电路的各输入端不能直接与高于+5.5V和低于-0.5V的低内阻电源连接,因为低内阻电源能提供较大的电流,导致器件过热而烧坏。

③除三态和集电极开路的电路外,输出端不允许并联使用。如果将 图T306双列直插集电极开路的门电路输出端并联使用而使电路具有线与功能时,应在其输出端加一个预先计算好的上拉负载电阻到VCC端。

④输出端不允许与电源或地短路。否则可能造成器件损坏。但可以通过电阻与地相连,提高输出电平。

⑤在电源接通时,不要移动或插入集成电路,因为电流的冲击可能会造成其永久性损坏。

⑥多余的输入端最好不要悬空。虽然悬空相当于高电平,并不影响与非门的逻辑功能,但悬空容易受干扰,有时会造成电路的误动作,在时序电路中表现更为明显。因此,多余输入端一般不采用悬空办法,而是根据需要处理。例如:与门、与非门的多余输入端可直接接到VCC上;也可将不同的输入端通过一个公用电阻(几千欧)连到VCC上;或将多余的输入端和使用端并联。不用的或门和或非门等器件的所有输入端接地,也可将它们的输出端连到不使用的与门输入端上。如图T307所示。

对触发器来说,不使用的输入端不能悬空,应根据逻辑功能接人电平。输入端连线应尽量短,这样可以缩短时序电路中时钟信号沿传输线的延迟时间。一般不允许将触发器的输出直接驱动指示灯、电感负载、长线传输,需要时必须加缓冲门。

(2)使用CMOS电路的注意事项

CMOS集成电路由于输入电阻很高,因此极易接受静电电荷。为了防止产生静电击穿,生产CMOS时,在输入端都要加上标准保护电路,但这并不能保证绝对安全,因此使用CMOS集成电路时,必须采取以下预防措施。

①存放CMOS集成电路时要屏蔽,一般放在金属容器中,也可以用金属箔将引脚短路。

②CMOS集成电路可以在很宽的电源电压范围内提供正常的逻辑功能,但电源的上限电压(即使是瞬态电压)不得超过电路允许极限值、…电源的下限电压(即使是瞬态电压)不得低于

系统工作所必需的电源电压最低值Vmin,更不得低于VSS。

③焊接CMOS集成电路时,一般用20W内热式电烙铁,而且烙铁要有良好的接地线。也可以利用电烙铁断电后的余热快速焊接。禁止在电路通电的情况下焊接。

④为了防止输入端保护二极管因正向偏置而引起损坏,输入电压必须处在VDD 和VSS之间,即VSS<u1<VDD。

⑤调试CMOS电路时,如果信号电源和电路板用两组电源,则刚开机时应先接通电路板电源,后开信号源电源。关机时则应先关信号源电源,后断电路板电源。即在CMOS本身还没有接通电源的情况下,不允许有输入信号输入。

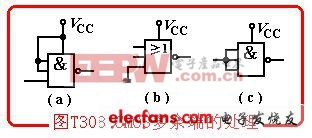

⑥ 多余输入端绝对不能悬空。否则不但容易受外界噪声干扰,而且输入电位不定,破坏了正常的逻辑关系,也消耗不少的功率。因此,应根据电路的逻辑功能需要分别情况加以处理。例如:与门和与非门的多余输入端应接到VDD或高电平;或门和或非门的多余输入端应接到VSS或低电平;如果电路的工作速度不高,不需要特别考虑功耗时,也可以将多余的输入端和使用端并联。如图T308所示。

以上所说的多余输入端,包括没有被使用但已接通电源的CMOS电路所有输入端。例如,一片集成电路上有4个与门,电路中只用其中一个,其它三个门的所有输入端必须按多余输入端处理。

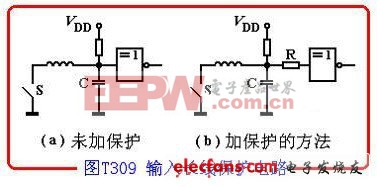

⑦输入端连接长线时,由于分布电容和分布电感的影响,容易构成LC振荡,可能使输入保护二极管损坏,因此必须在输入端串接一个10~20kΩ的保护电阻R,如图T309所示。

⑧CMOS电路装在印刷电路板上时,印刷电路板上总有输入端,当电路从机器中拔出时,输入端必然出现悬空,所以应在各输入端上接入限流保护电阻,如图T309所示。如果要在印刷电路板上安装CMOS集成电路,则必须在与它有关的其它元件安装之后再装CMOS电路,避免CMOS器件输入端悬空。

⑨插拔电路板电源插头时,应该注意先切断电源,防止在插拔过程中烧坏CMOS的输入端保护二极管。

上拉电阻相关文章:上拉电阻原理

评论