浅谈ARM内核MCU不同性能的决定因素

本文主要简述了决定ARM内核MCU的性能和功耗的主要因素。

继ARM推出Cortex-M0+内核后,其32位MCU内核增加到了4个。不久前,恩智浦也宣布取得了Cortex-M0+处理器授权,成为目前唯一一家能够提供完整的Cor tex-M0、Cortex-M0+、Cortex-M3和Cor tex-M4系列内核MCU的半导体厂商。飞思卡尔在今年3月份也已经推出了基于ARM Cortex-M0+的MCU Kinetis L系列。

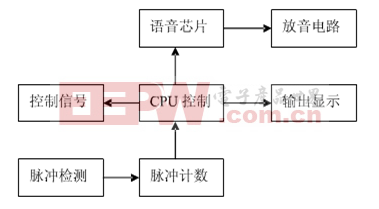

在ARM内核对MCU统一化进程的同时,各个厂商要怎样才能使得各自的产品与众不同、性能突出呢?恩智浦半导体的Jan JaapBezemer(全球微控制器产品线总监)表示,除了内核外,还有别的资源也能体现差异化,比如内存、数字/模拟IP等。Bezemer说:“有些IP是标准的,有些则不是。恩智浦公司花了很多时间来开发那些非标准的IP,为的就是能更好地将这些资源加以配置。此外,最应该注意的一点是降低内存的功耗,因为它是最耗电的单元。所有以上这些因素一起决定了MCU的性能和功耗。”MCU负责信号控制,所以对其而言,信号数据的传递效率就显得十分关键。而对信号数据的传递效率起决定作用的则是器件的架构。Bezemer对此强调:“我们是ARM 7内核处理器的最大供应商,这一点就足以证明我们器件的架构设计是非常成功的。并且我们的开发工具、软件和服务的支持等等也都是保证MCU产品实现差异化竞争力的重要因素。”

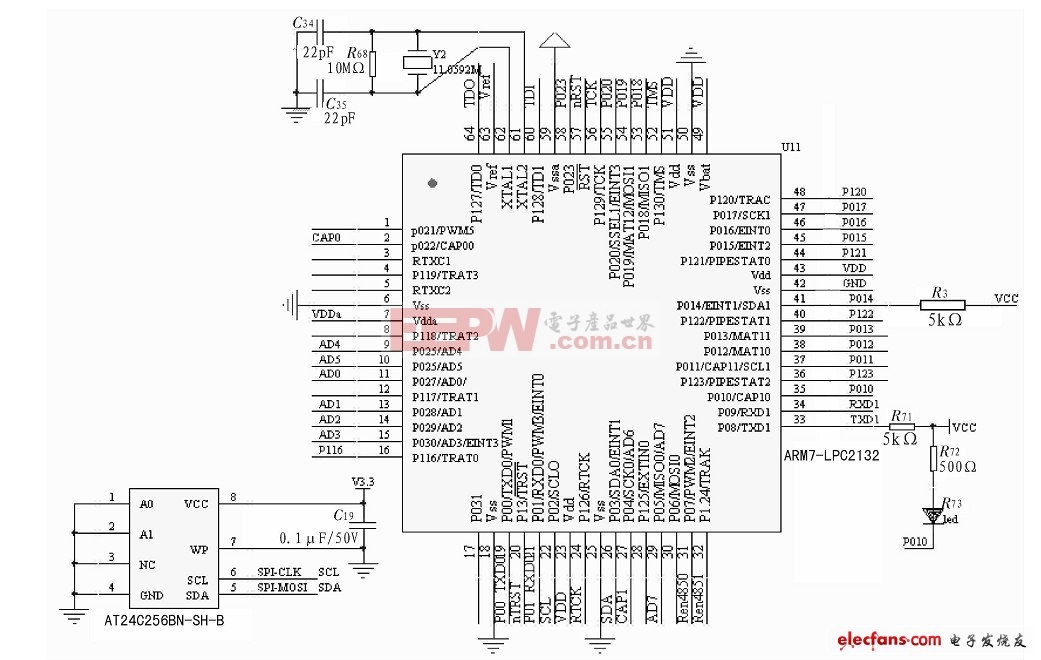

以恩智浦LPC11A00为例,在资源配置上都是Cortex-M050MHz的内核,但就是因为该器件在存储、串行接口、模拟子系统等方面的配置不同,便使之与其他同类内核MCU的性能有很大的差别。LPC11A00是业内唯一真正的EEPROM,它集成了32KB闪存,8KB的SRAM和4KB的EEPROM,同时还包括基于ROM的32划分的整数除法器以及I2C总线驱动程序;在模拟子系统中,还包含了8ch/10位ADC、10位DAC、模拟比较器、片内温度传感器、片内电压参考和UVLO(UndervoltageLockout)。

同样,恩智浦最新推出的基于Cor tex-M4的LPC4300在器件架构上也体现出的与众不同,使其特别适用于电机控制、太阳能逆变器、数字电源和音频等方面。LPC4300采用的Cor tex-M4+Cortex-M0的双核架构,目的在于减小Cortex-M4带宽占用,以便于内核专心处理数字信号控制应用中的数字计算,而把大量数据传输和I/O处理任务交给M0内核去处理。这种双核架构以及AHB总线矩阵大大提高了器件性能和效率,使其双核均可工作在204MHz上。Bezemer说:“这种架构类似MCU+DSP的体系。现在,在MCU中加入DSP功能和在DSP处理器中加入MCU功能是大势所趋。”

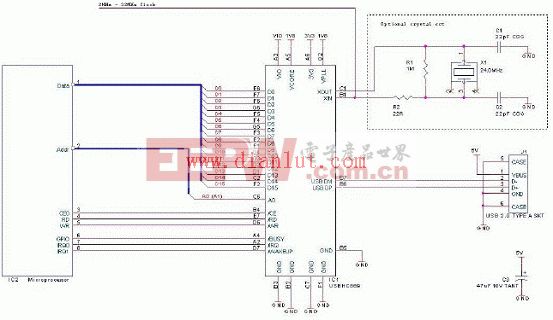

恩智浦开发出一种新型外设接口IP:SPI闪存接口技术(SPIFI),它是该公司基于Cor tex-M3 MCU的一个亮点,并被LPC1800采用。通过SPIFI可将外部串行闪存映射到MCU内存上,以至于实现片上内存读取效果。Bezemer表示:“SPIFI为设计人员提供了一种创新解决方案,在保持系统性能的同时达到简化配置、缩小封装体积、减少板载空间占用和节约系统成本的目的。关键在于,与片上闪存相比,外部闪存成本要低很多,并且这种方式可以不用CPU干预即可传送闪存和RAM的数据。”

以上强调的都是硬件设计上的差异化,其实软件的支持也是非常重要的。恩智浦向其所有LPC MCU客户免费提供了由德国SEGGER公司开发的emWin图形库软件(这款软件兼容单任务和多任务操作环境)。由于恩智浦的MCU全都集成了LCD控制器,因此在采用emWin后,UI设计可与固件开发分开进行。在固件开发的同时便可使用独立工具实现基本UI设计,以便提高LCD应用的设计速度。另外,像恩智浦这样基于Cortex-M0和M0+的MCU的开发以上海研发中心为主的这种基于本土设计为本土客户提供需求的产品也是十分重要的,因为这样的话,便与它们从本土走向全中国,挖掘更多的市场需求并寻求同本地IDH有更多的合作。

评论