多核DSP兼具ASIC和FPGA特性概述

由于ASIC解决方案NRE成本高,产品开发周期较长,在支持各种不同无线标准升级上灵活性不足。而FPGA的功耗对于高速、复杂运算而言要比ASIC和DSP加速器更高,同时在快速开发和调试上也难达到理想状态。基于此,TI近日针对无线基础设施应用而推出的DSP解决方案 SoC架构,基于C64x+多核DSP兼具ASIC处理能力和FPGA的灵活性,从而适应3G和4G无线基础架构设备制造商对高性能芯片的需求。

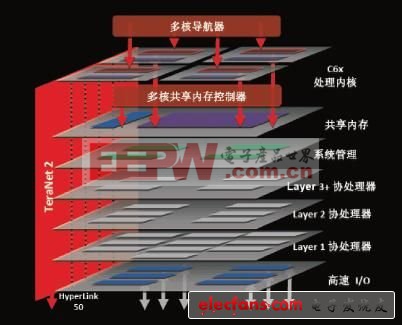

具有高度灵活性的可编程解决方案,同时兼具ASIC方案的优化特性,是TI面向无线基础设施市场开发的新一代DSP多核架构。基于40nm工艺的全新DSP架构主要特性包括:多核DSP可实现1.2GHz工作频率;增加的浮点支持4G多变量控制系统开发,可轻松实现对时间区隔和分频制的支持;全新多核导航器可实现DSP核、硬件加速器间数据的准确转移,同时提供带50Gbps的非封锁交换机架构外设,无需使用系统模块而满足了未来4G系统的要求;稳定的工具套件、针对具体应用的软件库和平台软件,为用户缩短开发周期提供更有效的调试和分析;运行频率高达1.2GHz、引擎性能为256 GMACS和128 GFLOPS的TI全新DSP架构实现了DMS性能5倍提升,同时将平均内核存储增加了2倍,保证了应用性能的稳定;提供高性能1层、2层网络协处理器。

全新SoC架构多核导航器(Multicore Navigator),利用8192任务型队列优化数据流的片上网络管理单元,支持内核与存储器存取之间的直接通信,省去了外设存取从而充分释放出多核性能。通过抽取可能影响多核系统中软件开发的诸多细节,极大地简化了程序模型。由于每个DSP内核均集成定点与浮点处理功能,通过提供内核间、硬件加速器间以及外设间的自动路径设置,每个内核彼此都可以不受核间冲突影响而独立工作,通常能为设计工程师节省3个月时间。多核共享存储器控制器设计方案,可加快片上及外接存储器存取速度;新架构还支持内核间动态系统调度并支持全内核授权,使得多核架构能类似于性能强大的单核系统。

这些适用于无线基站的4核器件,以及适用于媒体网关与网络应用的8核器件,TI预计将于 2010 年下半年开始提供样片。

评论