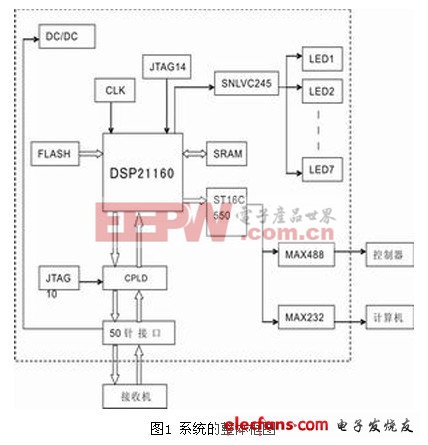

ADSP21160实现数字信号处理系统

程序加载:ADSP21160需要外接一个14针的JTAG接口,通过使用ADI公司提供的ICE仿真器,从计算机下载编制好的用户程序,装入ADSP21160的内部存储器或外接FLASH中。

外部器件选通:ADSP21160配置了/MS3~/MS0四个外部引脚,用于外部器件的选通。在同一时间,只其中允许一个有效(低电平)。这些引脚分别连接于FLASH、SRAM、并串转换芯片(ST16C550)的使能端,用于选通这些部件以及用于与外部接收机的数据通信。CPLD由于关系到数个器件的逻辑功能,故长期处于工作状态(使能端直接接地)。

3.FLASH加载及外扩存储器模块设计

FLASH加载模块:为了系统能够在上电后自动运行,为ADSP21160配置了外接FLASH。按照ADSP21160的用户手册,8位FLASH的数据线接DSP数据线的32_39位,地址线必须从ADDR0开始与ADSP21160相应地地址位直接连接。ADSP21160采用EPROM启动模式,用/BMS和/MS0相与后连接于FLASH的使能端。

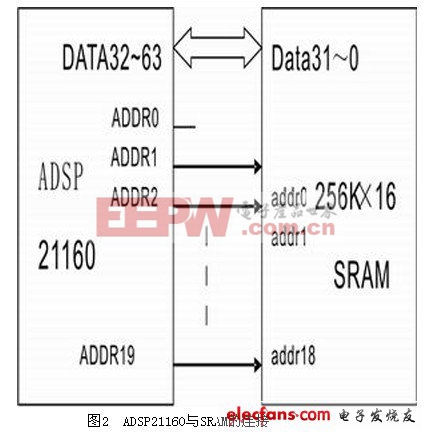

外扩存储器模块:ADSP21160是高性能的32位浮点处理器,对外最多可使用64位的数据总线。考虑到系统的精度要求及内部数据的处理模式,本系统对外只使用了32位的数据总线。这样,在外扩存储器的选择上,考虑到价格等因素,选用了两块256K×16位的SRAM并联构成32位的外扩存储器,如图2所示。

在地址线的连接上,和一般的接法梢有不同。由于ADSP21160规定,对外部空间的寻址,其奇地址通过低32位数据线传递;偶地址通过高32位数据线传递。考虑到在FLASH的连接上使用了DSP数据线的32_39位,为了简化今后PCB板的布线及充分利用SRAM的存储空间,在设计中,将ADSP21160的ADDR0的引脚悬空,将其ADDR1引脚与SRAM的addr0管脚相连,ADDR2与addr1相连,以下顺次连接。

外部通信接口模块设计

目标板通过一个50针接口与接收机相连,通过RD_REQ、RD_PMT、RD_EN、RD_CLK四根控制信号线进行,从接收机内部开辟的存储空间读取数据。

在本系统的设计中,其中间运算数据均采用32位浮点数,输出结果截取8位有效数字,通过并串转换器(ST16C550)转换成串行

评论