低功耗6管SRAM单元设计方案

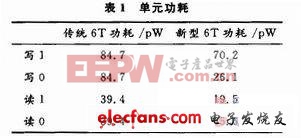

表1中可以看出,在传统的6T-sRAM读/写过程中,对称结构的两个位线电压的变化是一致的,因而功耗是相同的。新型6T-SRAM单元功耗比传统单元低了很多,这是因为在读/写操作的时候,参与工作的管子数量少,并且只有一个位线参与工作,并且在写0的时候,由于位线是0,所以功耗很低。

2.4 读/写仿真

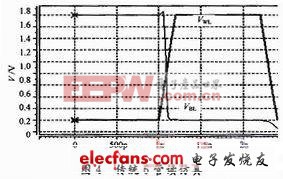

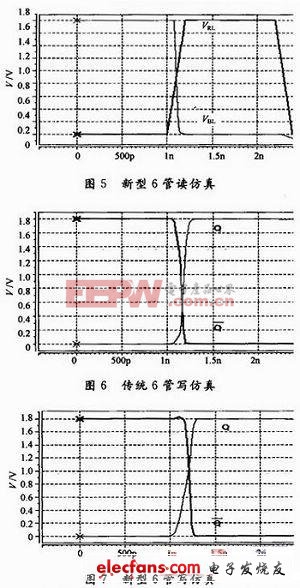

为了进一步验证新型6T-SRAM读/写功能的正确性,以及与传统6T-SRAM单元的比较,采用HSpice对两种管子进行了读/写仿真。如图4-图7所示。

新型6T-SRAM存储单元的读/写仿真表明,单个存储单元的读/写时间在0.2 ns内,符合存储器在高速状态下运行的需要。

3 结语

该SRAM单元是在0.18μm工艺下仿真的,新型SRAM采用漏电流保持技术,从而不需要刷新来维持数据,并且仿真显示功耗比较传统SRAM低了很多,读/写速度方面比传统SRAM慢了一点,但是这是在可以接受的范围内。

手机电池相关文章:手机电池修复

评论