TMS320C61416控制FPGA数据加载设计(一)

目前实现加载的方法通常有两种:一种是用专用Cable通过JTAG口进行数据加载,另一种是外挂与该FPGA厂商配套的PROM芯片。前者需要在PC机上运行专用的加载软件,直接下载到FPGA片内,所以掉电数据仍然会丢失,只适用于FPGA调试阶段而不能应用于工业现场的数据加载。后者虽然可以解决数据丢失问题,但这种专用芯片成本较高,供货周期也较长(一般大于2个月),使FPGA产品的开发时间受到很大约束。根据FPGA芯片加载时序分析,本文提出了采用通过市面上常见的Flash ROM芯片替代专用PROM的方式,通过DSP的外部高速总线进行FPGA加载;既节约了系统成本,也能达到FPGA上电迅速加载的目的;特别适用于在FPGA调试后期,待固化程序的阶段。下面以两片Xilinx公司Virtex-4系列XC4VLX60芯片为例,详细介绍采用TI公司的TMS320C61416 DSP控制FPGA芯片数据加载的软硬件设计。

1 Xilinx FPGA配置原理

Virtex-4系列的FPGA芯片外部配置引脚MODE PIN(M0、M1、M2),有5种配置模式,如表1所列。

FPGA在Slave SelectMAP方式下,共用了表2所列的15个配置引脚。

1.1 配置流程

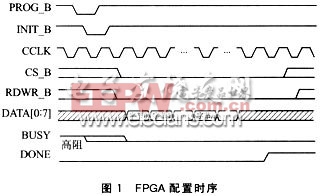

FPGA加载时序如图1所示。各配置信号必须满足其时序关系,否则配置工作无法正常完成。

图1中,Slave SelelctMAP加载主要包括以下3个步骤:

①启动和初始化。FPGA上电正常后,通过PROG_B引脚低脉冲进行FPGA异步复位,使得FPGA内部逻辑清零。其次PROG_B上拉高,停止外部复位,INIT_B引脚会在TPOR时间段内自动产生一个由低到高的跳变,指示FPGA内部初始化完成,可以进行数据下载;同时FPGA在INIT_B的上升沿采样其模式引脚MODE PIN,决定其模式配置。

②比特流加载。INIT_B信号变高后,不需要额外的等待时间,Virtex器件就可以立即开始数据的配置。比特流数据在外部CCLK信号上升沿按字节方式置入。该过程包括同步初始化字、器件ID号校验、加载配置数据帧、CRC校验4个部分。

③STARTUP启动。在成功校验CRC码位后,比特流命令使得FPGA进入STARTUP状态。它是由8相状态机实现的。中间包括等待DCM锁相、DCI匹配等几个状态,最后FPGA释放外部DONE引脚,对外输出高阻态,由外部上拉高,指示FPGA加载成功。

1.2 文件生成

ISE生成数据文件主要有3种:BIT文件,由二进制格式进行表征逻辑设计,包括文件头和配置数据,主要用于JTAG下载电缆模式;MCS文件,为外部PROM烧写生成的下载文件,ASCII码,与前者不同的是它含有在PROM中的数据地址和校验值;BIN文件格式,由二进制表示,完全由配置数据组成,不需要作其他的提取和进制转换,只是配置前的Byte-Swapped是在CPLD中实现的。本设计采用的是BIN文件格式。

评论