如何正确使用FPGA的时钟资源

时钟可以连接到FPGA上的一系列逻辑块上。为确保时钟信号在远离时钟源的寄存器上有合适的上升和下降时间(从而将输入输出时延控制在允许的范围内),需要在时钟驱动器和负载之间插入时钟缓冲器。DCM可用作时钟输入引脚和逻辑块之间的时钟缓冲器。

最后,还可以使用DCM将输入时钟信号转换为差分I/O标准信号。例如,DCM可以将输入的LVTTL时钟信号转换为LVDS时钟信号发送出去。

相位匹配时钟分频器

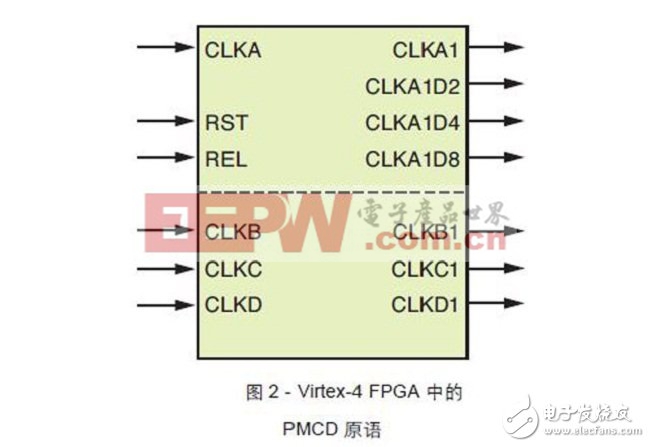

设计人员可使用相位匹配时钟分频器(PMCD)来生成相位匹配的分频输入时钟信号。这与分频时钟的DCM频率综合相似。PMCD还能生成设计中相位匹配但有延迟的时钟信号。在后一种情况下,PCMD能够在输入时钟信号和其它PMCD输入时钟信号之间保持边缘对齐、相位关系和歪斜。与DCM不同的是,在分频器的值可配置的情况下,赛灵思器件中现有的PMCD生成的时钟信号仅按2、4和8分频。这意味着PMCD生成的时钟信号的频率是输入时钟信号的1/2、1/4和1/8。在如Virtex-4FPGA这样的赛灵思器件中,PMCD紧邻 DCM并与其位于同一列上。每一列有两个PMCD-DCM对。因此DCM的输出可以驱动PMCD的输入。

由于DCM还负责处理去歪斜,因此只要不需要去歪斜时钟,设计人员就可以使用不带DCM的PMCD。通过专用引脚,还可以把一列中的两个PMCD连接起来。图2是 Virtex-4器件中的PMCD原语。详细内容请参阅Virtex-4FPGA用户指南(UG070,2.6版本)。

混合模式时钟管理器

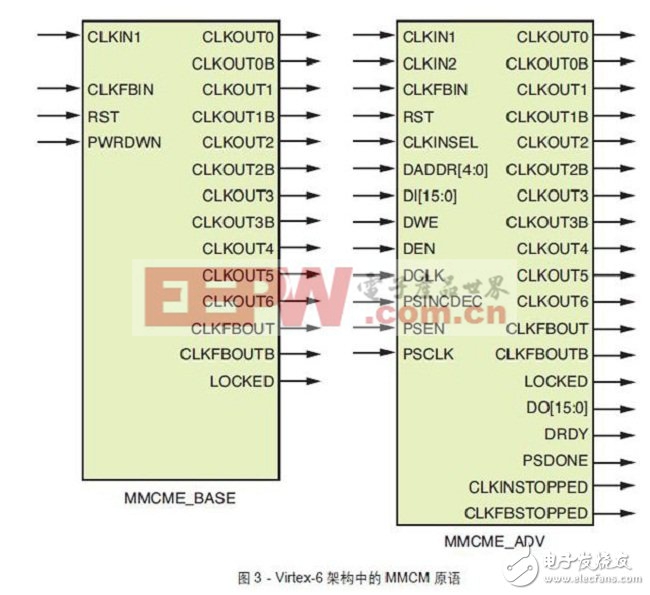

另一种类型的时钟资源——混合模式时钟管理器(MMCM),用于在与给定输入时钟有设定的相位和频率关系的情况下,生成不同的时钟信号。不过与DCM不同是,MMCM使用PLL来完成这一工作。Virtex-6FPGA中的时钟管理模块(CMT)有两个MMCM,而Virtex-7中的CMT有一个 MMCM和一个PLL。Virtex-6器件中的MMCM没有扩频功能,因此输入时钟信号上的扩频不会被滤波,将直接被传送给MMCM输出时钟。但 Virtex-7FPGA的MMCM却有扩频功能。

Virtex-6FPGA中的MMCM要求插入一个校准电路,以便在用户复位或用户断电后确保MMCM正确运行。赛灵思ISE设计套件11.5版本及更高版本能够在设计的MAP阶段自动插入必要的校准电路。若使用赛灵思ISE 的更早版本,则需要使用赛灵思技术支持部提供的设计文件手动插入校准电路。最后需要注意的是,在本移植该设计,以便用ISE11.5版本或更高版本实现时,必须手动移除校准电路,或通过适当设置每个MMCM上的综合属性,禁用自动插入功能。详细介绍请参阅赛灵思答复记录AR#33849。

对7系列器件中的MMCM就不存在这样的问题,因为这些FPGA只得到ISE13.1版本和更高版本以及新型Vivado设计套件的支持。Virtex-6系列中提供的MMCM间专用走线可便于用户将全局时钟资源用于设计的其余部分。

图 3显示了Virtex-6FPGA中的MMCM原语。各个端口的详细介绍请参阅Virtex-6FPGA时钟资源用户指南(UG362,2.1版本)。图 4显示了赛灵思7系列FPGA中的MMCM原语,有关详细介绍请参阅7系列FPGA时钟资源用户指南(UG472,1.5版本)。

fpga相关文章:fpga是什么

分频器相关文章:分频器原理 锁相环相关文章:锁相环原理

评论