EDA环境衔接测量软件 电子产品开发周期大幅缩短(一)

消费性电子产品汰换周期越来越短,且功能复杂度不断提高,使得系统研发人员面临缩短产品开发时间的严峻挑战。所幸,现今自动化测试系统已开始导入开放式FPGA,将有助EDA开发环境与测量软件的整合,让工程师可同时进行系统设计与测试,加快研发时程。

目前测试工程师所面临的最大挑战之一,即是个人观念局限于目前的技术中而停滞不前,因此,本文特别提供技术趋势的相关知识,针对测试与测量产业,探讨足以影响整个产业的重要技术与方法。

设计与测试并行为大势所趋

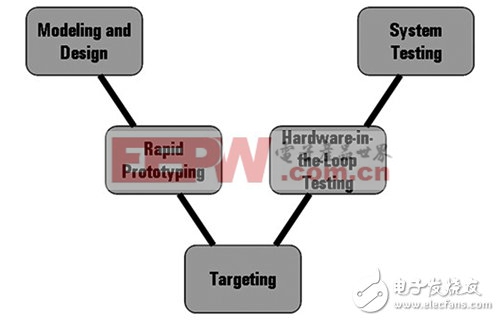

对目前的研发单位来说,缩短产品开发周期几乎是首要任务,特别是汽车与航空产业。要缩短开发时间的方法之一,就是同时进行设计与测试,这样的产品开发模式常以“V-diagram”模型(图1)表示。这些产业的最终产品,往往形成高复杂度“系统中的系统”;而V-diagram左边为“设计”,右边则为“测试”,其背后的概念,就是在开发出完整系统之前,先初步测试、检验子系统以达更高效率。只要是需要高度监控环境的产业,就常见到如V-diagram 的同步设计/测试方法,而且目前已有其他类型的装置或产业逐步采用相关实例。以半导体和消费性电子产业为例,其“短暂的产品使用周期”与“不断提高的产品复杂度”特性,都是缩短产品开发时间的瓶颈。

图1 V-diagram产品开发模型

根据2009年麦肯锡(McKinsey)针对半导体产业设计的问卷研究结果,半导体产业“产品生命周期”几乎是汽车产业的叁分之一而已。另一份麦肯锡问卷研究亦指出,半导体新产品设计的平均开发时间约为19个月,因此,研究人员归纳出“研发完整度(RD Excellence)”为加速开发时程的主要关键。

基于商业需求,产品开发过程必须更重视研发完整度,因此电子产业已越来越趋向设计与测试并行。要强化此实例的主要方式,就是提高电子设计自动化(EDA)模拟软件与测试软件之间的连结。

提高EDA/测试软件连结

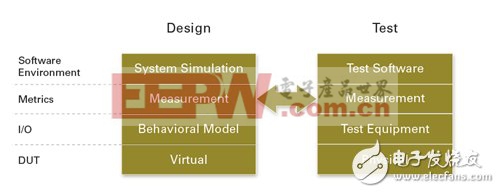

若要了解模拟软件在产品设计流程中的角色,必须先了解软件在产品开发的“设计”与“测试”阶段有何作用。在初始的设计/模拟期间,EDA软件可针对模拟产品的物理或电子行为(Electrical Behavior)建立模型(图2)。EDA软件基本上属于公用程式,即根据一系列的输入,透过数学模型而呈现受测物(DUT)的输出,再将相关度量结果提供予设计工程师。

图2 软件于产品开发阶段所扮演的角色

在开发产品的检验/认证阶段,软件使用条件仅有些许不同,主要是能自动测量实际的塬型即可。但检验/认证阶段所需的测量演算法,亦与EDA软件工具所使用的演算法相同,这点则和设计/模拟阶段类似。

目前EDA软件正在发展中的功能,就是要于EDA环境与测试软件之间,提高软件连结功能的层级。更进一步解释,这种连结功能就是要让现有的EDA软件环境可驱动测量软件,并且测量自动化环境可自动连结EDA设计环境。

衔接设计与测试软件环境的优点之一,即于设计程序的初期,软件即可提供更丰富的测量演算法。工程师不仅可于设计初期进一步了解自己的设计,其模拟作业亦能整合检验/认证程序所取得的资料。第二项优点,则是让测试工程师在设计程序中,即可加速开发有用的测试程序代码,以利缩短复杂产品的上市时间。

<

评论