基于DSP的列车应变力测试系统设计方案

存储器接口设计考虑的主要问题是:如何采用EP2ROM+高速RAM的配置方式来实现存储子系统。

EP2ROM用来存放测试系统的程序和初始化数据,系统加电运行时,TMS320VC33自动将程序和初始化数据从低速EP2ROM装载到高速RAM中。装载完毕后,程序在高速RAM中全速运行。系统中存储器装载程序和初始化数据的EP2ROM起始地址为400000h。同时系统中还扩展了64K高速RAM,起始地址为100000h。此外,片选信号由系统中CPLD来实现。

对于TMS320VC33与EP2ROM的接口,系统采用一片AM29F040 (512K×8)实现了8位数据宽度的程序引导。EP2ROM占用的地址空间为400000h~47FFFFh。读EP2ROM时插入的等待周期由软件来控制。

TMS320VC33实时运行时的程序和数据都存放在快速RAM中,因此快速RAM与TMS320VC33必须实现零等待接口。根据时序要求,当TMS320VC33工作于60MHz时钟时,快速RAM的存取速度必须小于13ns。本测试系统采用的快速RAM是IS61LV6416-8T,存取速度为8ns。由于这种快速RAM的数据宽度是16位,而TMS320VC33的数据宽度是32位,因此必须采用两片构成32位数据宽度,并令写使能信号与经过译码的写信号相连,输出使能信号与译码后的读信号相连。测试系统中的快速RAM占用的地址空间为0x100000~0x110000。

通信子系统

在应变力测试系统中,为了把TMS320VC33对采样信号的处理结果通过串口传送到PC机显示或作进一步处理,设计中采用TI 公司的TL16C550扩展异步通信芯片将DSP与PC机相连,以完成测试系统与PC机之间的通信。

在TL16C550与TMS320VC33的串行通信中,虽然可以通过查询的方式工作,但这样会降低系统的性能。本设计通过TMS320VC33的RXRDY和TXRDY引脚引入外部中断,从而使系统工作在中断方式,保证了TMS320VC33与PC机的高速通信。

此外,本测试系统利用TL16C550的串行通信接口与上位PC机完成信息的交换。此时由于RS-232电路电平与TTL电平不同,因此必须经过电平转换,设计中采用MAX232A来完成这一功能。

可编程逻辑器件—译码模块

测试系统中的译码模块主要用来实现DSP对片外存储器、I/O设备进行管理以及根据DSP提供的地址信号,给外部存储器、I/O设备分配不同的地址空间。对于本测试系统而言,编码方式主要考虑的是TMS320VC33的接口能力问题。TMS320VC33的地址空间总容量为16M,采用统一编址也不会对存储器容量造成太大的威胁。另外,TMS320VC33没有专门的I/O指令和I/O端口总线,因而测试系统中采用的是统一编码方式,并用ABLE语言

设计译码电路。

测试系统软件设计

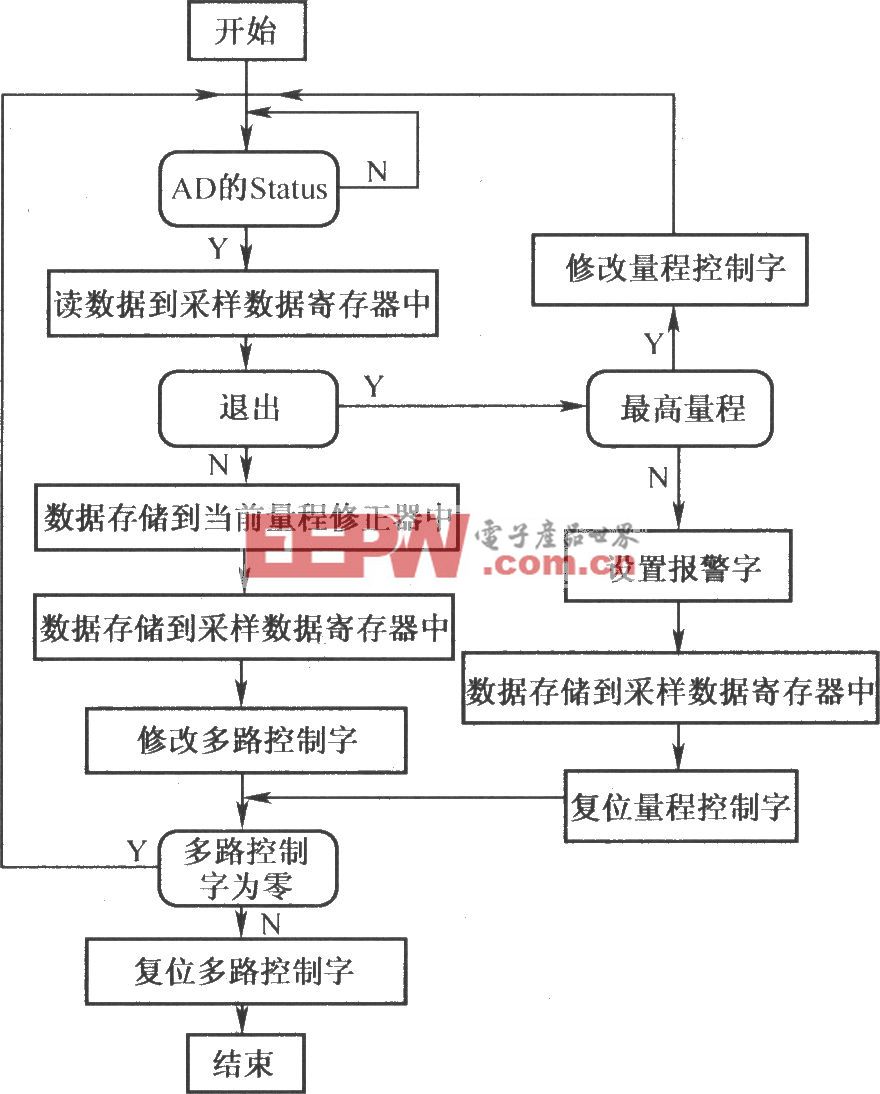

测试软件算法的优劣直接关系着整个测试系统的性能。本测试系统的软件流程如图3所示。

测试程序首先进行整个系统的初始化工作。在完成系统初始化后,系统处于查询状态,查询是否完成新的数据采样,数据采样程序在中断程序中完成。当系统完成一次A/D转换后,向TMS320VC33申请中断,TMS320VC33响应中断,在中断服务程序中读出转换结果并设置标志:EXINT=1,通知主程序采样完成。主程序在查询到EXINT=1后,对数据进行处理,处理结果通过TMS320VC33的并行口经并/串转换送给PC机的串口,并把标志EXINT设定为0,开始下一轮采样等待。

信号完整性

评论