得益于PMIC的功能渐强,移动设备续航能力见增

封包追踪技术的目标,在于改善功率放大器承载较高波峰平均功率比讯号的效率。要在有限的频谱资源内提供高资料处理能力,必须使用有着较高波峰平均功耗比的线性模组。很不幸的是,传统电压源固定的功率放大器,在这些情况下运转时效率都较低。在封包追踪的功率放大器中,可藉由改变功率放大器供应电压,与无线频率讯号的封包同步,进而改善其效率。

节省电路板空间 PMIC整合音讯晶片

OEM也面临节省电路板空间的压力,他们必须释放出更多的面积以容纳新功能,同时还要维持装置的轻薄短小并降低成本。针对这些目标,三维(3D)封装或是晶片堆叠技术的使用能产生优势。一般而言,晶片堆叠是利用低密度接线或焊锡凸块连接不同堆叠层。业界在单一封装中整合或堆叠完全可配置PMIC及低功耗音讯编解码晶片(Audio CODEC),在单晶片上整合超过四十个不同高低电压的电路及类比功能,大幅节省电路板空间及成本。

不只节省空间,业界音讯编解码晶片还能为消费装置提供理想的音讯效能。藉由在数位讯号处理器(DSP)内整合先进回音消除软体,音讯编解码晶片能过滤背景杂音并增加声音清晰度,如此一来,即使是在吵杂的环境中也能提供丰富、低频及高清晰的频率。

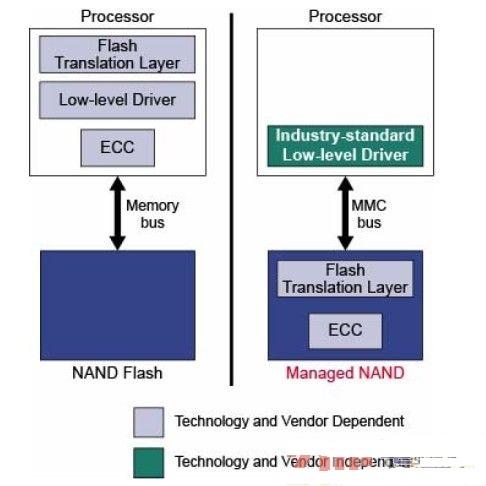

除晶片堆叠技术外,未来业界将看见其他节省电路板空间新技术。其中一种技术是3D整合,是透过直通矽晶穿孔(Through-Silicon Via, TSV)连接不同电路层,TSV较为密集且能提供更强大的连接能力,可以跨越更多层并节省更多电力。3D整合一开始是被用来封装高速记忆体及SoC,用来为绘图功能提供更优异的频宽,而它现在绝对是未来值得被好好观察的领域。

轻薄特色恐引发高漏电流

行动装置尺寸愈趋轻薄短小,但却装入比以往更多功能。更细小的元件尺寸可能会引发高漏电流的危险性,这是短通道效应及不同的掺杂水平所致,而这最终会让产业无法朝更小的尺寸迈进。

此外,新堆叠材料的出现例如高介电常数金属闸极(HKMG),以及鳍式场效电晶体(FinFET)此类完全空乏型电晶体(Fully Depleted Transistor)。现在的FinFET是3D结构,在平面基板上升起,相较于同样面积的平面闸,FinFET可以提供更大的容量。通道周围的闸门能提供优秀的通路控制,如此一来,当元件处于断开状态时,能通过主体的漏电流就微乎其微。这让低临界电压值的使用可行,以实现最佳切换速度及功率。

还有许多其他有潜力的技术蓝图。例如,戴乐格(Dialog)与台积电共同合作最先进的0.13微米(μm)Bipolar-CMOS-DMOS(BCD)技术,用于在小型单晶片电源管理晶片中整合先进逻辑、类比及高电压元件,以支援下世代的智慧型手机、平板电脑及Ultrabook。

BCD制程技术代表驱动半导体产业各领域,包括应用端、设计及制程持续前进的创新力量。此技术在同一片晶圆上结合类比Bipolar(B)元件、互补金属氧化物半导体(CMOS)以及双重扩散金属氧化物半导体(Double Diffused Metal Oxide Semiconductors, DMOS)。系统设计师采用此技术,减少功率损失、电路板空间及成本。该技术有助于制造更好、更小及更创新的产品。同时,由于现在的BCD技术是以6寸晶圆制造,晶圆厂能让他们几乎折旧完毕的产线得以继续贡献生产力,如此能减少终端客户的成本并产生利润,或是能拥有投资其他新兴技术的更多空间。

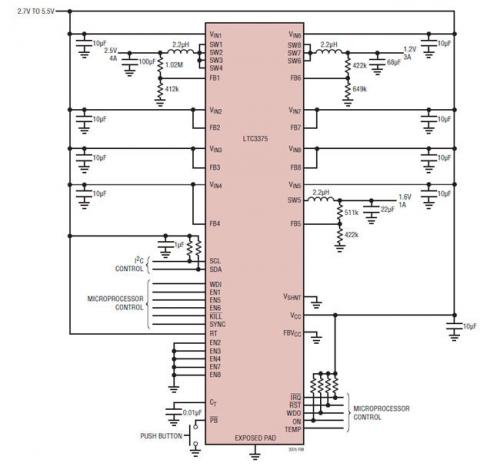

直流对直流(DC-DC)电源转换器是现今电源管理积体电路的基础元件。业界专利的TIPS(Transformative Integrated Power Solutions)技术采用一种以交换电容技术为基础的独特转换方法。该项技术允许使用较小的导电元件,除提升效率之外,并且可以达到比竞争技术更高的整体电源密度,为可携式和资料中心应用提供显著的优势。

电源管理决定品牌成败

根据产业预测,行动运算装置需求正持续增加。行动装置正从个人资讯装置进化为行动运算平台,对日常需求扮演愈来愈重要的角色。与此同时,电源效能正迅速成为这个时代的关键问题。智慧型手机使用者若高度满意手机电池寿命,相较于不满意的使用者,前者再次购买同品牌手机的可能性较高。在高度满意手机电池寿命(在10分量表中选择10分)的4G智慧型手机拥有者中,有将近25%的人表示「一定」会再次购买来自同一家制造商的手机。相较于此,在较不满意

评论