最详尽32位MCU低功耗设计考量与经典范例参考(二)

制程选择

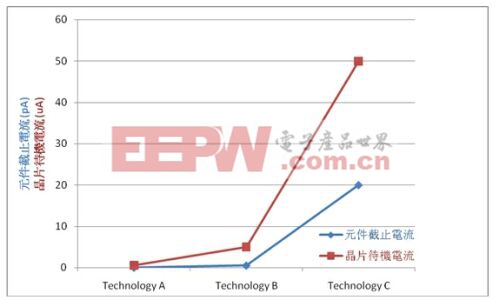

为了达到低功耗的运作,并能有效地在低耗电待机模式下,达到极低的待机功耗,可以透过对制程的选择而站上基本的要求门槛。在不强调速度极致的某些制程分类,选择极低元件截止电流制程(如下图)进行逻辑闸制作,并进行数位设计是方法之一。选择这种策略的额外效益是,通常也能在降低动态操作电流上,达到较佳的表现。另外,由于高温大幅增加静态电流,当温度由摄氏25度增加到摄氏 85度时,一个典型比例约增加 10 倍的静态电流,以非低功耗 0.18 微米制程开发的 32 位元 MCU,逻辑阀门数 200K、4KB SRAM 在核心电压 1.8V、摄氏25度的静态耗电约为 5 ~ 10 微安,当温度升高到摄氏 85度时,静待电流将会飙高到 50 ~100 微安。而低功耗制程在摄氏85度仅约 10微安静态电流。

低功耗高效能的 CPU内核

早期低功耗 MCU 受限于成本及制程技术,大都选择 8 位元 CPU 内核,但随着工业上的智能化也在展开,如远端监控,数位化、网路化等。简单说来,就是人物之连结(云端应用)、物物之连结(物联网) 需求越来越多,导致产品功能越来越复杂,运算量越来越高,8 位元 MCU 已逐渐无法满足效能需求。 为了兼顾低功耗高效能,选择适用的 32 位元 CPU 内核乃大势所趋。

选择低功耗CPU 内核,除了单位频率耗电流外,还需要综合考量紧凑的低记忆体代码,相同功能所需的代码越长,除了增加记忆体成本,也代表更长的运行时间及功耗。另外,由于软件开发成本在后期将会越来越高,大量的参考代码及更多的第三方开发商的支持,都可以有效降低软件的开发时间及成本。所以选择一款更多人使用的 CPU 内核也是重要的考量之一ARM Cortex-M0阀门数仅 27K,使用的电量在 1.8V,超低泄漏 180ULL (Ultra LowLeakage) 仅约50μA/MHz。M0 内核采用Thumb2指令集架构,产生出非常紧凑的低记忆体代码,进一步降低了电源需求。ARM自 2009 年发表了32位元Cortex-M0内核以来,包括 NXP、新唐科技、ST、Freescale等多家国内外 MCU 大厂相继投入Cortex-M0 MCU 开发,不论供货或者品种的齐全度都已十分成熟,投入Cortex-M0的 MCU 开发商也在持续增加中。

低功耗数位电路

对于一般的同步数位电路设计,要使数位单元有效降低操作电流,透过控制时钟的频率或截止不需要的时钟跳动,也是重要的方法。低功耗MCU通常配备丰富的时钟控制单元,可对各别的数位周边单元,依照需求做降频或升频的操作调整,在达到运作能力的同时,用最低的频率来运行。但为了达到更弹性的时钟源配置,可能导致 CPU 内核和周边电路时钟不同步的现象,此时必须仔细考虑电路设计,保证跨时钟领域资料存取的正确性。

另外为了尽量降低 CPU介入处理时间或降低 CPU 工作频率而节省下来的功耗,可以提供 DMA 或周边电路相互触发电路进行资料的传递,例如Timer 定时自动触发 ADC 或 DAC,并透过 DMA 进行资料由 ADC 到 RAM 或者 RAM 到 DAC 的搬移,同时在 ADC 的输入可以增加简单的数字绿波及平滑化电路,如此不须要 CPU 经常介入处理,也不会因为需要即时处理 ADC 或 DAC 事件导致中断程序占用太多时间,降低系统的实时性及稳定性。

支援多种工作模式

为了配合不同的应用需求,并达到系统平均功耗的最小化,低功耗 MCU需要提供多种操作模式,让使用者灵活调配应用,常见的操作模式有下列数种:

正常运行模式:CPU 内核及周边正常工作,能即时改变 CPU 及周边的工作频率 (On the Fly) 或关闭不需要的时钟源以获得最佳的工作效能。

评论