MC68332与AT93C46的SPI接口时序问题

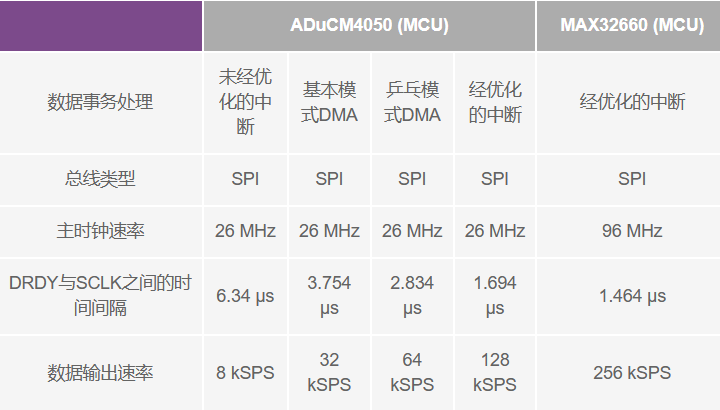

在微机自动化设计中,随着总线速度越来越块,芯片的上升/下降沿越来越陡,时序问题变得越来越突出。时序问题在设计中是至关重要的,尤其是随着时钟频率的提高,留给数据传输的有效读写窗n越来越小,要想在很短的时间内,使数据信号从驱动端完整地传送到接收端,就必须进行精确的时序计算和分析。同时,时序与信号的完整性也是密不可分的,良好的信号质量是确保时序稳定的关键。由于反射、串扰造成的信号质量问题,都很町能带来时序的偏移和紊乱,导致时序余量不够。

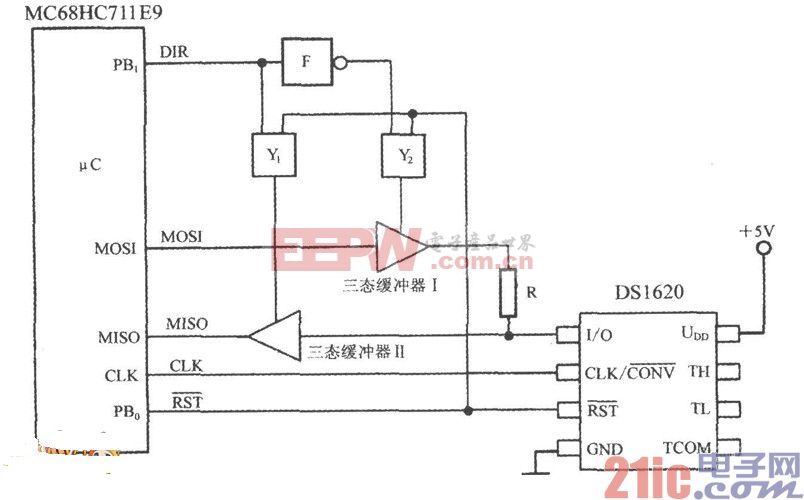

1 MC68332与AT93C46的SPI接口

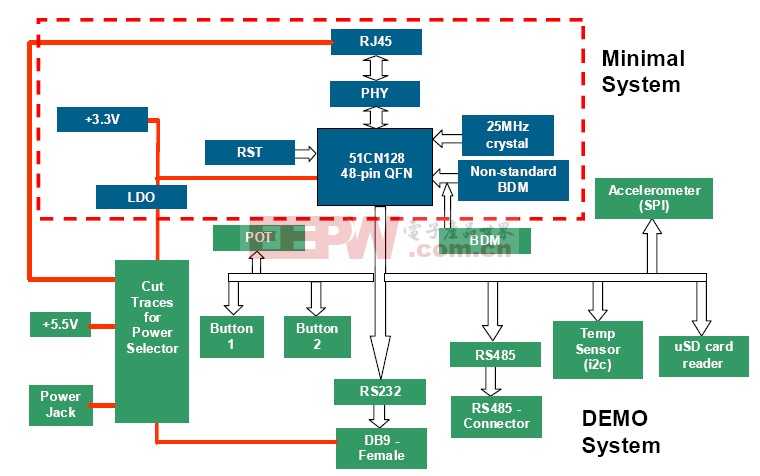

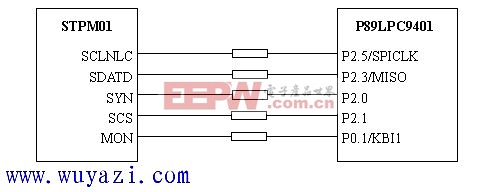

MC68332与串行存储器AT93C46的硬件接口比较简单,如图1所示。其中,MC68332的CS、CLK(和MOSI脚为SPI输出;MISO脚为SPI输入。

2 时序问题提出

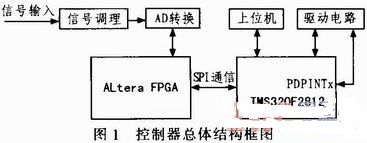

在调试过程中出现批次不同的AT93C46,读数据都能正确进行。但写数据时,有的批次写正确,有的则出现错误。下面分析MC68332与AT93C46 SPI接口的写时序图(如图2所示)及参数(见表1)。

图2中,tDIS为数据建立时间,AT93C46数据手册要求其最小值为10Ons;tDIH为数据保持时间,要求其最小值为100 ns。

MC68332手册中,tDIS最小值为5Ons,tDIH最小值为50ns。

可见tDIS数据建立时间不够,也就是说在MC68332写出的数据还没有稳定的情况下,SK时钟的上升沿已经来到。这时,AT93C46会将不稳定的数据进行锁存。这样,大部分情况下锁存的数据是错的。

3 时序问题解决

时序余量不够一般有两方面原因:一是系统本身各芯片时序参数不匹配;二是信号完整性差,导致时序余量减少。为解决数据建立时间不够的问题,将MC68332的SPI接口的MISO数据入,MOSI数据出,CLK时钟信号接入EPLD中进行时序调整。将CLK信号的上升沿向后平移,下降沿向前平移,使得建立和保持时间都加长。在EPLD中调整建立和保持时间后,任何批次的AT93C46都能正确读/写。图3和图4分别是时序调整前后示波器的波形图。

结语

在微机自动化系统的设计中,应将充足的时序余量设计作为重中之重,这样才能保证系统稳定、可靠地运行,且不必因芯片速度变快而更改设计。

评论