大容量闪存芯片与DSP接口设计

关键词:接口;闪存;TMS320F2812

在有些智能仪器中,需要实时存储大量的采样数据,以提供历史数据查询。这需要采用大容量、低功耗、可以快速重复擦写的非易失性存储器,因此选择闪存作为数据存储介质, 即使系统掉电,而所采集到的数据仍能长时间的保持,不丢失。

在本文的设计中采用的是TI的TMS320F2812和三星的闪存K9K2G08U0M。K9K2G080M是三星公司的大容量闪存芯片,它的单片容量高达256MB,属于NAND FLASH结构。传统存储器结构及引脚信号定义方式难以解决存储容量增加的矛盾,即存储容量的增加使得系统的连线复杂并且可靠性降低。NAND FLASH存储器将数据线与地址线复用为8 条I/O线, 另外还分别提供了命令控制信号线, 命令、地址和数据信息均通过8 条I/O 线传输,因此, NAND FLASH存储器不会因为存储容量的增加而增加引脚数目,从而极大方便了系统设计和产品升级,升级到更大容量而无需更改外部连接。因此,本文讨论的NAND FLASH存储器在单片机应用系统中的硬件连接和软件编程方法具有较大的参考价值。

1 K9K2G08U0M 简介

电源电压为2.7 -3.6V,读速度为80ns;

具有指令/地址/ 数据复用的I/ O 口;

NAND FLASH 的存储结构以页面为单位,能使芯片的读取速度更快。由2048个大小相同的存储块组成,每个块由64页组成,每页2K字节和64个空闲字节;

1.2 K9K2G08U0M的引脚说明

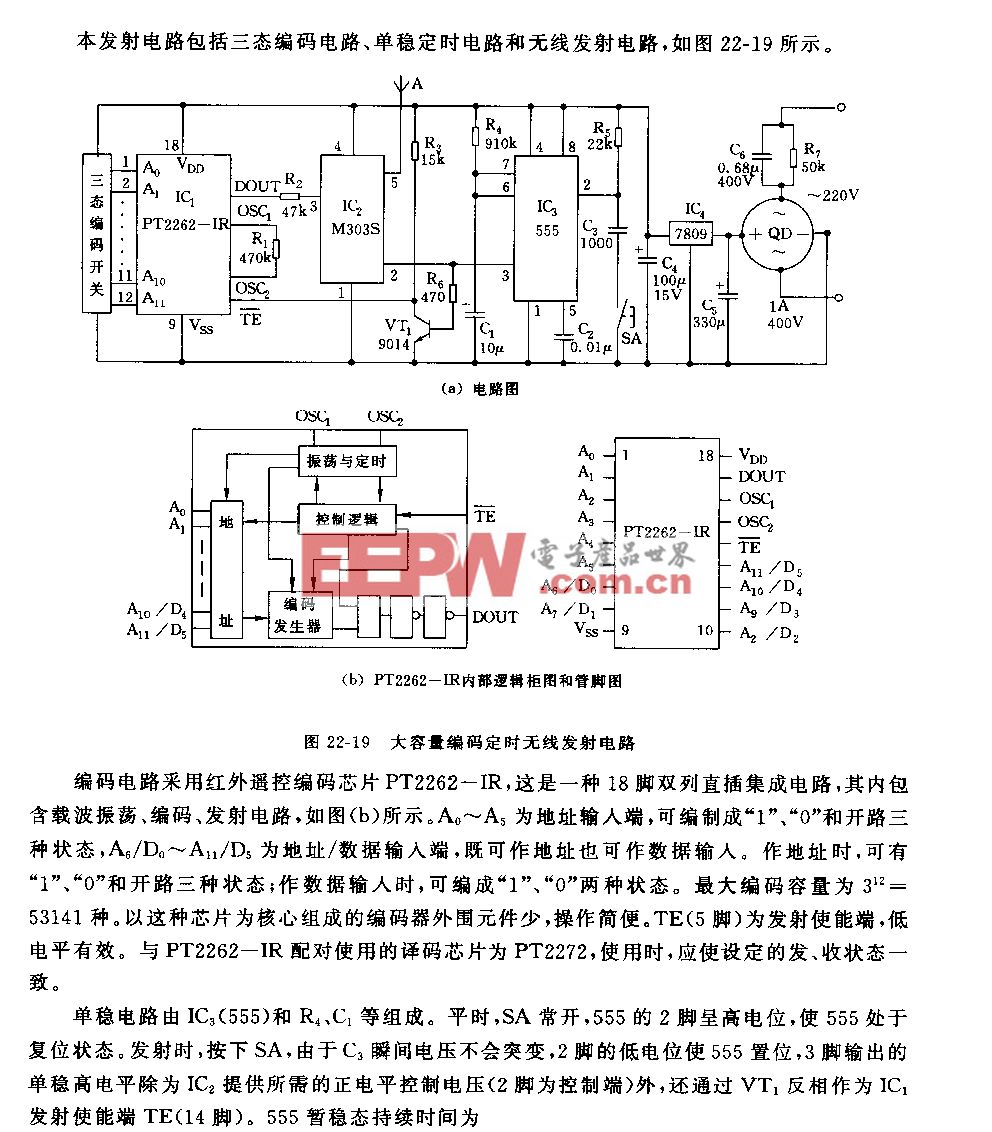

图1 为引脚功能图,各引脚的功能如下:

图1 K9K2G08U0M引脚描述

I/ O0~I/ O7 : 三态,输入命令、地址和数据以及读操作时输出数据。当芯片没有被选中或不能输出时, I/ O 口处于高阻态。

CLE: 命令锁存使能。为高电平时,命令通过I/O 口线在WE 信号的上升沿被锁入命令寄存器。

ALE: 地址锁存端,在WE 上升沿且ALE 为高电平时,地址锁存。

CE: 片选端, 用于控制芯片的选择。当芯片忙时, CE 为高电平而被忽略, 此时芯片不能回到备用状态。

RE: 读使能端。在RE的下降沿,输出数据有效, 并且它还可以对内部数据地址进行累加。

WE: 写使能端,通过该端口可以在WE 脉冲的上升沿将指令、地址和数据进行锁存。

WP: 写保护端,在电源电压变化期间,在WP 为低电平时,可产生写/ 擦除保护。

R/ B : 就绪/ 忙输出, R/ B 的输出能够显示芯片的状态。R/ B 处于低电平时,表示有编程、擦除或随机读操作正在进行。操作完成后, R/ B 会自动返回高电平。

2 DSP与FLASH的硬件接口

TI的TMS320F2812采用统一寻址方式,扩展的外部存储器K9K2G08U0M既可以作为程序存储器,也可以作为数据存储器。具体接口如图2所示。

图2 DSP与闪存接口

TMS320F2812的外部存储器接口包括:19位地址线,16位数据线,3个片选控制线及读写控制线。这3个片选线映射到5个存储区域,Zone0,Zone1,Zone2,Zone6和Zone7,其中Zone2的片选线是CS2,存储区域是:0x080000-0x0FFFFF,512K*16位。当对存储区域Zone2访问时,Zone2的片选线CS2低有效。

K9K2G08U0M 没有地址线,命令、地址和数据信息均是通过闪存的I/O0-I/O7传输,另外,虽然K9K2G08U0M的容量达到了256MB,远远大于了TMS320F2812的存储区域Zone2的容量1MB,但由于访问flash的地址是通过I/ O 口输入,不需要通过地址线寻址,因此无需考虑采用页面技术解决逻辑存储空间与物理空间的映射问题,大大简化了DSP与FLASH的硬件接口。

由于K9K2G08U0M本身具有功能管脚较少的优点,因此跟DSP的连接也相对简单。DSP和FLASH的工作电压均是3.3V,因此两者的引脚可以直接连接,不需要进行电平转换。K9K2G08U0M 的ALE、CLE分别由DSP 的A1 和A0 控制。DSP的低8位数据线直接与闪存的I/O0-I/O7 相连,实现命令、地址和数据的传输; DSP的通用I/O口IOA2 接R/B,监测存储器的工作状态,当R/ B 处于低电平时,表示有编程、擦除或随机读操作正在进行;操作完成后, R/ B 会自动返回高电平。DSP的W E 、R D 分别接FLASH的W E 、R E , 控制读、写操作。CS2接闪存的片选线CE。

3 对FLASH操作的软件设计

本系统的DSP 编程采用了C 语言,首先定义了三个变量FLASH_D,FLASH_A,FLASH_C作为数据,地址和命令寄存器用来对FLASH读写数据,地址和命令。

#define FLASH_D 0x08fff0 #define FLASH_A 0x08fff2 #define FLASH_C 0x08fff1

因为K9K2G08U0M 的ALE、CLE分别由DSP 的A1 和A0 控制,所以当向命令寄存器FLASH_C写数据的时候,访问的是DSP的存储区域Zone2, 此时Zone2的片选线低有效,FLASH被选中,地址线A0变高,而引脚CLE高电平有效,此时写到FLASH_C的数据(FLASH命令)通过I/O写到闪存。同理,向FLASH_A和FLASH_D写可分别实现向FLASH写地址和数据。这样设计时,通过简单的写三个存储器即可分别实现命令,地址和数据锁存,符合操作时序。

对FLASH的操作主要包括:按页读操作,页编程,缓存编程,块擦除,读状态,复位等。FLASH芯片的读写有其特点,读写操作都要以扇区为单位进行,擦除操作是以块为单位,由于对FLASH写数据时,位数据只能由1变为0,因而对FLASH进行写操作前必须把写单元所在块擦除;因此写操作时,所要擦除块的数据必须事先保存,然后再对该块进行擦除,并把数据写到指定单元,最后把其余部分恢复过来。因此FLASH芯片的写操作比较复杂,需要开辟一定的缓冲区对要擦除的块进行保存。

图 4 页编程流程

下面仅以页编程为例简要介绍对FLASH的操作过程,页编程时序如图3,图4为其流程框图,函数为void page _ program();

页编程时,首先写页编程命令80H,可将数据写入到FLASH缓冲区, 然后顺序输入待编程存储器的地址共5字节,2字节Column Address 和3字节Row Address,以及待写入的数据。页编程命令10H用于实现数据从缓冲区到FLASH的编程操作。待R/ B 变为高后,系统将读状态寄存器,以判断写操作是否成功。写命令时,CLE 要有效;写入地址时,ALE 要有效;写入数据时,CLE、ALE都必须无效。I/ O0~I/ O7 上的命令、地址、数据通常是在WE 的上升沿锁存的。I/ O0等于0表示页编程成功,否则页编程错误。

void page_program_flash()

{ unsigned char *Flash_E;

unsigned char temp;

unsigned int i;

Flash_E=FLASH_C;

*Flash_E=0x80;

Flash_E=FLASH_A;

*Flash_E=coladdr1;

*Flash_E=coladdr2;

*Flash_E=rowaddr1;

*Flash_E=rowaddr2;

*Flash_E=rowaddr3;

Flash_E=FLASH_D;

for(i=0;i2048;i++)

{ *Flash_E=i; }

Flash_E=FLASH_C;

*Flash_E=0x10;

flash_delay();

do{ Flash_E=FLASH_C;

*Flash_E=0x70;

Flash_E=FLASH_D;

temp=*Flash_E;

temp=temp0x41;

}while(temp!=0x40);

}

}

4 结束语

本文详细介绍了闪存K9K2G08U0M与DSP 的硬件接口技术和软件编程。由于NAND FLASH具有的优点使得硬件接口设计和软件编程比较简单,升级也比较容易。NAND FLASH 具有非易失性、大容量、低成本等优点,在数码相机,MP3等数码电子产品和智能仪器得到越来越广泛的应用。本文作者创新点:直接用DSP地址线A0、A1分别控制FLASH的命令锁存CLE和地址锁存ALE,并在此基础上定义了数据,地址和命令寄存器用来对FLASH读写数据,地址和命令,这相当于间接对CLE和ALE进行操作,简化了软件编程设计。

参考文献

[1] 苏奎峰. TMS320F2812原理与开发. 北京:电子工业出版社,2005.4

[2] SUMSUNG ELETRONICS. K9K2G08U0M / Flash Memory.

[3] 谷葆春 K9F56XXXOB系列FlashMemory的存储组织与操作实现.微计算机信息.2004年4期 115―117页

评论