基于CC―NUMA的多处理器系统研究

对于多处理器系统,比较流行的有3种模式,对称多处理(Symmetric Multiprocessing,SMP)模式、非均匀存储访问(Non Uniform Memory Access,NUMA)模式、大规模并行处理(Massively Parallel Processing,MPP)模式。SMP模式即将2个或2个以上的同样的处理器连接到一个共享的主存上。在SMP系统中,所有的处理器可以同时访问同一个物理存储器,即运行同一个操作系统,因此也被称为均匀性存储访问系统。这种结构比较简单,但是由于其是共享存储器,容易在访存时产生系统瓶颈,可扩展性也比较差。MPP是分布式存储器模式,可扩展性好,但是需要并行编程和并行编译,在软件系统构建上比较复杂,使用不便。NUMA架构将若干个单元通过专门的互联设备联结在一起组成分布式和共享内存空间。每一个处理器可以访问自己的存储器,也可以访问其他处理器或者共享的存储器,所有访存有远近、时延长短之分,称为非均匀存储访问。在某个处理器访问空间上比较远的存储器时,会有很大的时延,为了缓解这个问题,通过高速缓存一致性使得处理器访问存储器的几率大大降低,在某种程度上提高了系统效率,这种架构称为CC―NUMA即一致性缓存非均匀存储访问模式。这种架构继承了SMP和MPP系统的一些优点,在处理器个数,内存大小、I/O连接能力和带宽上有很大的伸缩性,又保持了SMP系统单一操作系统、简单的应用程序编程模式和易于管理的优点。

本文引用地址:http://www.amcfsurvey.com/article/202701.htm1 CC―NUMA基本架构

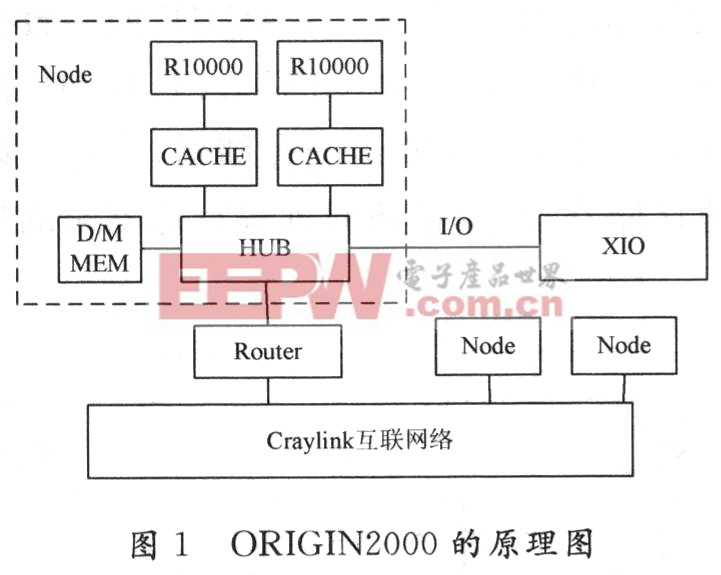

CC―NUMA架构的系统最出名的莫过于SGI公司的ORIGIN系列,SGI公司很好的发展和扩展了CC―NUMA技术,其基本架构被广泛应用。图1是其ORIGIN2000的基本原理图,每一个节点拥有2个处理器,2个二级缓存,主存,用于互联的HUB芯片,1个I/O接口,1个互联网络的路由器接口,它的每个节点可以看作是一个SMP,通过互联网络可扩展至128个处理器的多处理器系统。Origin 2000的所有结点通过CrayLink高性能互联网络相互联接,路由器是构成CrayLink的基本单位,它包含6个端口,内部采用交叉开关实现端口间的全互联。每个路由器的2个端口用于联接结点,其余4个端口实现路由器间的互联,形成互联网络拓扑结构。该CrayLink的半分带宽与结点个数成线性递增关系,对任意2个结点,至少能提供两条路径,保证了结点间的高带宽、低延迟联接和互联网络的稳定性和容错能力。

2 两种比较新的架构

SGI公司的Origin系列多处理器系统是一种比较通用的架构,但是还是比较复杂。后来,分别由Corepaq公司的Alpha EV7框架的处理器Alpha 21364和AMD公司的Opteron处理器组成的CC―NUMA架构的多处理器系统简单很多,这两种处理器都是针对多处理系统领域推出的,其有着特有的专为多处理器系统应用设计的处理器结构。

2.1 Alpha 21364处理器

2000年,Compaq公司推出了Alpha处理器的第四代产品Alpha21364,这是一款RISC处理器,在当时非常先进,在业内首次在处理器内集成了内存控制器,特别是它还有先进的多处理互联功能,在建造多处理器系统上很方便。

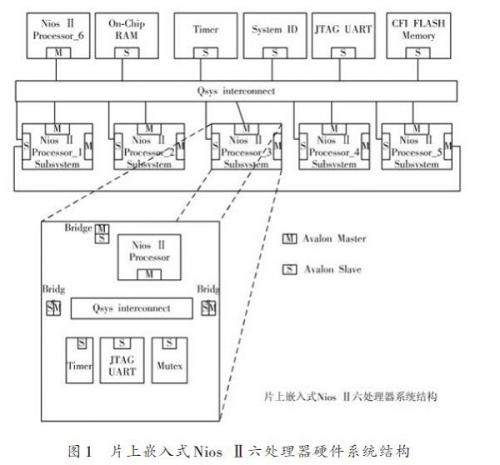

21364的简化图如图2所示。21364是64位处理器,拥有1.5 MB的L2 CACHE,支持缓存一致性协议。内部集成了2个RDRAM内存控制器,在RDRAM中对于页命中点对点的延迟是30 ns,加载应用的延迟是75 ns,对应高达12 GB/s的带宽。最大的不同就是有一个路由器,有4个连接通道可与附近处理器相连,并与本地端口和I/O端口相连,每个连接通道提供6.2 GB/s的带宽。

21364的处理器问互联总线提供了CC―NUMA多处理器架构间的无粘合连接,如图3所示。处理器间的二维拓扑互联架构满足了最远的处理器间的最小系统延迟设计。这种架构可扩展至128个处理器互联。

2.2 Opteron处理器

AMD公司在2001年推出了其第8代处理器K8架构的Opteron处理器。Opteron处理器基于X86系统架构并对其做了根本性改善,属于64位处理器,并兼容32位X86处理器架构。Opteron处理器集成了内存控制器,降低了访存延迟,加大了访存带宽。Hyper―Transport(超传输)互连控制器也被集成到Opteron处理器内部,在处理器和I/O子系统之间提供了拓展性极强的数据连接带宽。在Opteron处理器内部的数据通道为双向16位的通讯,可以达到1 600 MT/s(每秒百万次传送)的工作效率,可提供双向为6.4 GB/s的带宽。AMD Opteron处理器之间以及处理器同I/O子系统之间如何通过HyperTransport(超传输)技术进行互连。处理器之间的互连采用的是一致性协议(CoherentProtocol),相反I/O连接遵循的是非一致性协议(Non―coherent Protoco1)。集成了3个HyperTransport(超传输)互连控制器和1个内存控制器的处理器,需要尽可能高效地把指令和数据信息发送到相关接口。为实现这一需求,系统采用了交叉通道架构。

评论