串行数据转换器接口

问:我应该在什么时候选择具有异步串行接口的数据转换器?

答:异步通信方式允许设备之间交换信息,不必借助于时钟。为了使用相同的数据格式 ,必须对设备初始化,其中包括设置一种传输速率(通常用波特率表示,或位数每秒)。还应 该规定转换结果如何开始传送和结束传送。我们使用容易识别的带有起始位和停止位的数据 序列来传送数据。传送过程还包括奇偶校验位,用来检测设备出错。

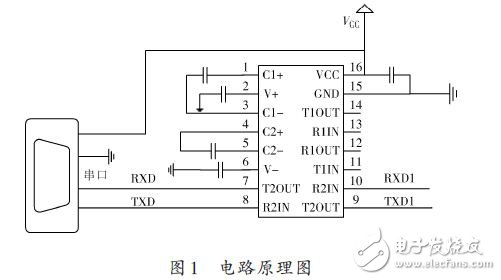

图106示出了AD1B60数字化信号调节器与PC机异步通信端口之间的接线图。这是一种3 线双向接口(为了简明,地线省去未画)。应该注意发送线与接收线在线路的另一端位置交换 。

图106 AD1B60与PC机之间的异步通信接口

异步通信线路对仅限于设备分散式通信应用场合是很有用的。因为在每次传送中都包 括起始位和停止位,所以设备在任何时间只要输出其数据就可以开始通信。另外设备之间 的接线数目也减少了,因为时钟和控制信号线都不需要了。

问:有一种ADC产品说明在串行接口中推荐使用非连续时钟,为什么?

答:这种技术要求可能是指ADC在转换过程期间要求其时钟信号无效。有的ADC有这种要 求,因为连续的时钟信号能够馈送到ADC的模拟部分,反过来会影响转换结果。如果I/O端 口有一个帧脉冲,那么连续的时钟信号在转换期间可能变成不连续。这个帧脉冲用作门控信 号,只有在数据传递时才允许将串行时钟送到ADC。

问:如何使设备与SPI或MICROWIRE接口标准兼容?

答:SPI(串行外围接口)与MICROWIRE分别是美国摩托罗拉公司和国家半导体公司研制的 串行接口标准。大多数同步串行式数据转换器都很容易与这两种接口连接,但是在有些情况 下可能需要附加连接逻辑(glue logic)。

问:好,我放弃偏见,在我的当前设计中决定使用串行ADC。我按照产品说明的技术要求 刚刚把线路接好。当用MICROWIRE标准转换结果时,ADC的输出好像总是FFF HEX (不论 模拟输入电压如何变化),这是怎么回事?

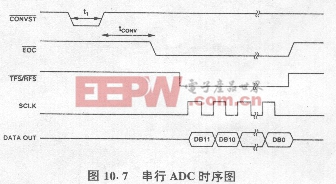

答:这或许是通信问题。首先我们需要检查ADC与处理器之间的连接问题,即定时和控制 信号线是否接好。我们还需要检查一下处理器的中断结构。与时序有关的可能误差有许多。你要想检查这个问题,首先将所有的时序信号要么接到逻辑分析仪上,要么接到多通道示波 器 上(至少需要3个通道才能同时检测全部时序信号)。你在仪器的荧光屏上应该观察到类似图1 0.7所示的时序图。首先保证从微处理器或从独立的信号源产生一个启动转换命令CONVST) 。常见的错误是所施加的CONVST信号极性不对。虽然也能启动转换,但不是按照你期望的时 序转 换 。另外应该记住的是,通常要求CONVST信号有一个最小的脉冲宽度(典型值约为50ns)。一般 来自快速微处理器的写脉冲或读脉冲宽度都不能满足这个要求。如果脉冲宽度太窄,可用软 件方法插入等待周期来增大脉冲宽度。

图107 串行ADC时序图

其次应该保证在读周期开始之前微处理器一直在等待模数转换完成。为了使微处理器产 生中断信号,你的应用软件应该知道完成A/D转换所需要的时间,或等待ADC转换结束(EOC) 发出的指示信号。还要保证EOC信号极性正确,以免ADC在转换进程中会产生中断。如果微处 理器对中断不响应,你应该检查软件中断的设置。

另外,如果转换器寻址不对,检查一下串行时钟序列(SCLK)的状态也是很有必要的。正 如 前面的讨论所述,有些DAC和ADC在连续时钟作用下,工作不正常。除此以外,还有些DAC和A DC要求SCLK在某一指定状态总得有一个闲音(idles)。

问:我现在已经发现了我的软件中的问题和一些解决方法,使问题有所改善。当改变输 入电压时,ADC输出的数据也发生变化,但是转换结果好像不可识别,这是怎么回事?

答:可能产生的误差源仍然很多。ADC的转换结果或者直接用二进制数据形式表示,或者 用2的补码形式表示(BCD码用得不太多)。为了使微处理器接受合适的数据格式,应该检查它 的配置。如果微处理器的配置不能直接接受2的补码,你应该将转换数据与100…00二进制数 进行异或操作,将其转换成二进制数。

通常利用串行时钟的前沿(上升或下降沿)选通ADC的数据输出并且进入数据总线。然后 利用时钟的后沿使数据进入微处理器。应该保证微处理器与ADC在同一转换条件下正常工作 ,保证所有准备时间和保持时间都满足要求。如果串行ADC的转换结果恰好是期望值的一半 或二 倍时,这是一个告警信号,它说明这个数字结果(尤其是MSB)是由于受错误的时钟边沿作用 。同样一个问题,对于串行DAC则表现为其输出电压恰好为期望值的一半或二倍。

驱动转换器的数字信号应该干净。过冲或欠冲除对器件可能引起长期损坏以外,还能产 生转换误差和通信误差。图108示出了用来驱动单电源转换器的时钟输入 具 有很大过冲的尖脉冲信号。在这种情况下,时钟输入驱动PNP晶体管的基极。按照惯例,将 器件的P型衬底内部连接到最负的电位,这里为地。在SCLK线上大于地电位以下03V的幅度 完 全能使N型晶体管的基极和P型衬底之间的寄生二极管开始导通。如果经常出现这种情况,而 且作用时间很长,可能会导致器件损坏。

图108 过冲或欠冲波形及其损坏器件的机理

评论