一种超低功耗、容错的静态随机存储器设计

摘要:为了减轻辐射环境中静态随机存储器(SRAM)受单粒子翻转(SEU)的影响以及解决低功耗和稳定性的问题,采用TSMC 90 nm工艺,设计了一款可应用于辐射环境中的超低功耗容错静态随机存储器。该SRAM基于双互锁存储单元(DICE)结构,以同步逻辑实现并具有1 KB(1 K×8 b)的容量,每根位线上有128个标准存储单元,同时具有抗SEU特性,提高并保持了SRAM在亚阈值状态下的低功耗以及工作的稳定性。介绍了这种SRAM存储单元的电路设计及其功能仿真,当电源电压VDD为0.3 V时,该SRAM工作频率最大可达到2.7 MHz,此时功耗仅为0.35μW;而当VDD为1 V时,最大工作频率为58.2 MHz,功耗为83.22μW。

本文引用地址:http://www.amcfsurvey.com/article/202329.htm关键词:静态随机存储器;双互锁存储单元;单粒子翻转;电路设计

作为半导体存储器大家族的主要成员,SRAM是世界上应用最广泛的存储器,它是数字处理、信息处理、自动控制设备中不可缺少的部件。随着空间技术的快速发展,越来越多的SRAM器件被应用到各类航天器和卫星的控制系统中。这些电子系统的微电子器件,除了具有高可靠性要求外,还需要具有低功耗以及抗辐射能力。随着晶体管特征尺寸的不断减小,集成电路集成度和速度的提高,芯片的功耗也越来越大,然而高功耗会降低电路的可靠性并影响芯片的使用寿命。所以大规模集成电路(LSI)需要降低功耗并提高其可靠性。一些研究报道表明,减少半导体器件整体功耗的一个有效途径是降低电源电压(VDD),因此使VDD降低到亚阈值范围可以使CMOS晶体管达到良好的超低功耗性能。然而随着VDD和阈值电压的降低,SRAM功耗降低,工作速度得到提高,但同时也对存储单元的静态噪声容限(SNM)产生不利的影响。SNM是使存储单元状态翻转的最小直流噪声电压,其决定了存储单元的稳定性和SRAM的可靠性,影响SNM的因素主要有电源电压,工艺缺陷和寄生电阻。具体设计中,尽量避免SNM下降的问题,在兼顾速度和功耗的前提下,以提高SNM,提高存储单元的稳定性。在某些情况下,甚至需要牺牲一些功耗来实现高稳定性。

同时在辐射环境中的高能粒子(质子、中子、a粒子和其他重离子)轰击微电子电路的敏感区时会引发单粒子效应(Single Event Effect,SEE)。辐射效应可能会引起电路工作的瞬时扰动,可能会改变电路的逻辑状态,甚至引起器件和集成电路的永久损伤。这种由于粒子轰击时产生的单粒子效应而改变存储单元的逻辑状态的现象,称为单粒子翻转。本文提出一种基于DICE的存储单元,该结构在实现低功耗高稳定性的同时,有效的克服了SEU效应。

对于整个SRAM设计而言,存储单元是设计的核心,它对芯片的面积和功耗起主要作用,同时还影响工作的稳定性,可靠性和速度。同时存储单元也是对辐射效应最为敏感的部分,本文研究的超低功耗容错存储器就是基于这两种目的设计的,超低功耗以及抗SEU。

1 基于DICE结构的SRAM单元电路的设计

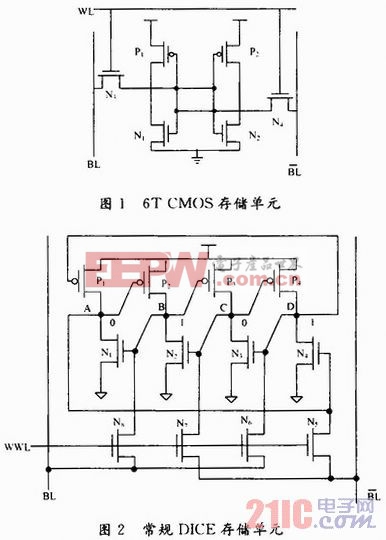

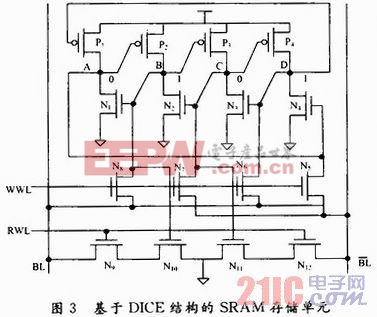

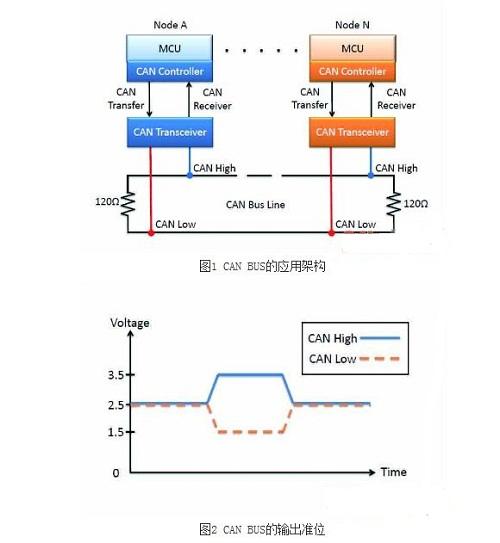

抗辐射SRAM的设计主要有两种思路:一种是采用特殊的工艺进行加固,如外延、SOI、SOS等;另一种是采用设计方法进行加固。随着信息化时代的到来,人们提出了多种设计加固的SRAM单元电路,电路设计加固技术得到了辐射效应领域的广泛认可。常规SRAM器件的基本存储单元通常由6个晶体管(6 TRANSISTORS,6T)结构双稳态触发器组成如图1所示,不能满足空间抗辐射要求。在加固存储单元的设计中,DICE结

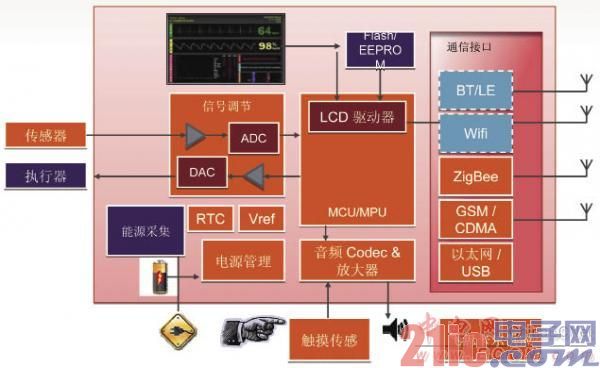

构(如图2所示)能够有效地减轻SEU效应,本文采用一种新型的基于DICE结构设计的SRAM存储单元,它能实现抗SEU效应,提高系统的稳定性,并保持在亚阈值电压下SRAM低功耗的特点。

1.1 存储单元概述

基于DICE结构设计的SRAM存储单元如图3所示,该单元由16T组成,其中DICE结构(N1~N4,P1~P4)比DICE结构多加的4个晶体管(N9~N12)用来进行读操作,N5~N8用来进行写操作。该存储单元有两个字线,WWL为写字线用来进行写操作,RWL为读字线进行读操作,控制传输管开关。BL与分别为位线和反位线。在正确的读过程中,BL维持在它的预充电值,BL与上产生电位差,经过灵敏放大器放大后输出,从而实现从存储单元中读出存储值。该单元采用一个四节点冗余结构,四个节点(A,B,C和D)保存着两对互补形式的数据(亦即:“1010”或“01 01”),这些数据通过传输门同时进行读或写操作。DICE单元通过双节点反馈控制实现抗单粒子翻转。这意味着四个节点中的每一个节点的逻辑状态均由相邻的两个节点控制(如:A通过P2控制B并通过N1控制D,B通过P3控制C并通过N1控制A等)。8个单管反相器形成2个反馈环:顺时针P管反馈环P1~P4和逆时针N管反馈环N4~N1。假设存储单元处于“1”状态(见图3),两个反相器圈(N4~P1和N2~P3)处于导通状态,形成两个锁存器(每个锁存器由两个交叉耦合的反相器组成)。而N1~P2和N3~P4处于截止状态。N1~P2和N3~P1这4个晶体管构成2对双向反馈电路并完成反馈互锁功能,将N4~P1和N2~P3这两个锁存器隔离开。值得指出的是,由于反馈机制的存在,该SRAM单元具有很强的抗读翻转能力。

1.2 状态分析

电路中,假设存储单元处于保持状态,同时数据以“0101”形式被存储(即节点A,B,C和D分别保存数据“0101”)如图3所示。如果一个粒子撞击晶体管N2,此时N2上产生一个瞬态电流,使得节点B的电压由高变低。那么,晶体管P3被打开从而驱动节点C。但是,由于晶体管N3的驱动能力强于晶体管P3,这一变化仅仅使节点C的电压略有增加。同时,节点B的电压由高变低又会使晶体管N1关断,而节点A被晶体管P1和N1的漏电流所驱动。如果在瞬间发生极短时间的翻转,节点B的电压将保持原值。如上所述就是发生单粒子瞬态时的过程。

评论