MRAM:RAM和NAND再遇强敌

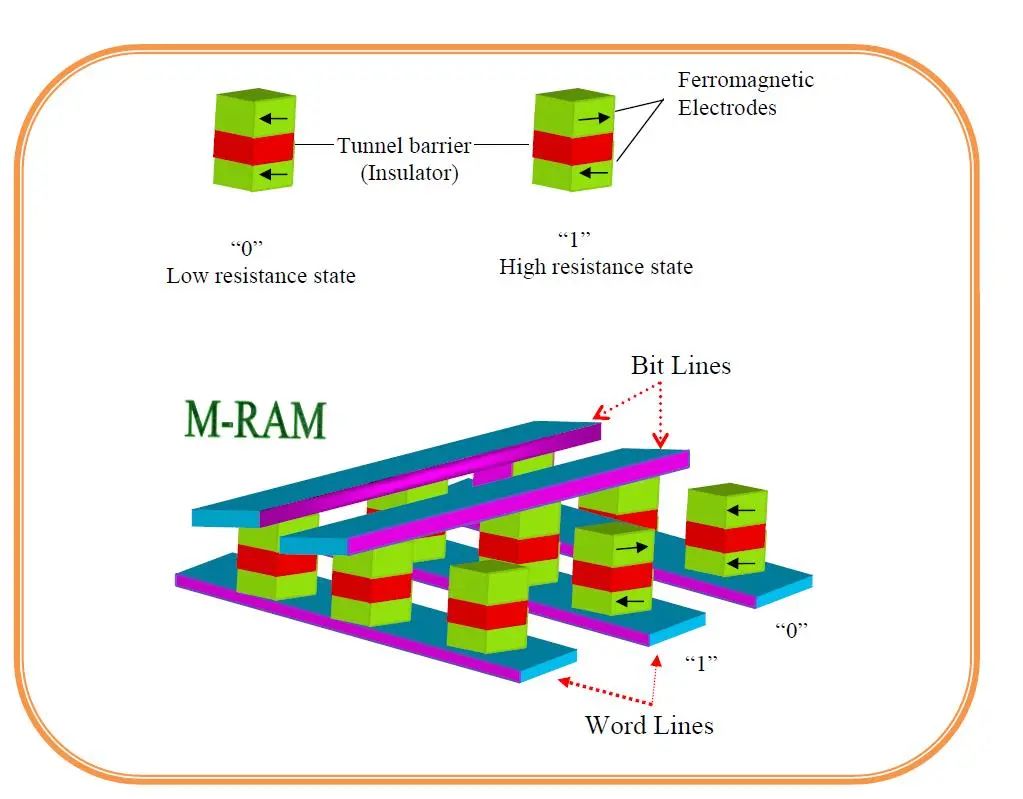

M 是一种非易失性存储技术,通过磁致电阻的变化来表示二进制中的 0 和 1,从而实现数据的存储。由于产品本身具备非易失性,让其在断电情况下依然可以保留数据信息,并拥有不逊色于 DRAM 内存的容量密度和使用寿命,平均能耗也远低于 DRAM。

本文引用地址:http://www.amcfsurvey.com/article/202311/453218.htm被大厂看好的未来之星,非它莫属。

三星:新里程碑

目前三星仍然是全球专利第一,2002 年三星宣布研发 MRAM,2005 年三星率先研究 STT-MRAM,但是此后的十年间,三星对 MRAM 的研发一直不温不火,成本和工艺的限制,让三星的 MRAM 研发逐渐走向低调。2014 年,三星与意法半导体签订 28nmFD-SOI 技术(一种与 FinFET 齐名的技术)多资源制造全方位合作协议,授权三星在芯片量产中利用意法半导体的 FD-SOI 技术。当年,三星成功生产出 8MbeMRAM,并利用 28nmFDS,在 2019 年成功量产首款商用 eMRAM。2020 年,三星首批基于 eMRAM 的商用产品上市,由其制造的 Sony GPS SoCs(28nm FDSOI) 被用于华为的智能手表,以及由台积电采用 22nm 超低漏电制程 (ULL) 制造的 Ambiq 低功耗 MCU。

2022 年 12 月,三星在著名的微电子和纳米电子会议 IEEE 国际电子器件会议 (IEDM) 上发表了一篇题为"面向非易失性 RAM 应用的全球最节能 MRAM 技术"的论文。该论文介绍了基于三星 28 纳米和 14 纳米逻辑工艺节点的面向非易失性 RAM 的产品技术。作为对该论文所分享的杰出研究和突破性成果的认可,该论文被选为 IEDM 存储器类别的亮点论文。凭借这一认可,三星达到了一个新的里程碑。

具体而言,增强型磁隧道结(MTJ)堆栈工艺技术大幅降低了写入错误率(WER)。此外,MTJ 还从以前的 28 纳米节点提升到 14 纳米 FinFET 工艺,实现了 33% 的面积缩放。这种芯片级尺寸允许在同一晶圆上生产更多芯片,从而产生更多的净芯片。此外,它还使读取周期时间缩短了 2.6 倍,16Mb 的封装尺寸也缩小到了 30 平方毫米,是目前业界最小的商用尺寸。该解决方案在-25°C 温度条件下可提供超过 1E142 个周期的近乎无限的耐用性。不过,最重要的成就可能还是同类最佳的能效,在 54MB/s 带宽条件下,主动读取和写入功耗分别为 14mW 和 27mW。

三星电子 eMRAM 的两大新成就是开关效率提高和 MTJ 扩展。开关效率是衡量 eMRAM 性能的关键指标。例如在 8Mb 阵列上重复进行的单位 WER 测试结果表明,芯片中的 WER 分布降低了 20%。通过应用 MTJ 堆栈工程,可以验证 WER 达到个位数 ppb5 水平。

eMRAM 的第二大成就是改进了 MTJ 扩展。在 eMRAM 架构中,由于开关电流与 MTJ 位面积成正比,因此有必要减小 MTJ 的尺寸,以降低每个位的写入能量。然而,在 MTJ 缩放过程中,由于单元电阻的增加和变化,耐久性和读取裕度都会下降。在创新和独创性方面,三星的研究团队对隧道势垒工艺进行了重大改进,将电阻面积减少了 25%,短故障率降低了 2.75 倍。与闪存型 eMRAM 相比,通过将 MTJ 的尺寸缩小 25%,降低了 NVM 型 eMRAM 的有源写入电流,同时还确保了 MTJ 尺寸控制所需的足够制造余量。

三星目标是到 2026 年实现 8 纳米制程,到 2027 年实现 5 纳米制程。

MTJ 在后端(BEOL)金属布线工艺之间形成,不会影响逻辑基线,从而使 MRAM 能够在 MTJ 工艺变化最小的情况下缩减到 FinFET 节点。利用这一优势,三星正在从 28 纳米 eMRAM 技术升级到 14 纳米 FinFET 工艺。这种 14 纳米 eMRAM 目前正在开发中,符合 AEC-Q1007Grade1 标准(汽车半导体可靠性测试的全球标准)。目标是在 2024 年之前完成开发。

此前三星披露了其开发业界首个 5 纳米 eMRAM 的计划。除了到 2024 年推出 14 纳米 eMRAM 之外,该公司还计划到 2026 年和 2027 年分别推出 8 纳米和 5 纳米 eMRAM,进一步扩大其 eMRAM 产品组合。与 14 纳米工艺相比,8 纳米 eMRAM 的密度预计将提高 30%,速度提高 33%。

这项内存技术有望引领电动汽车和自动驾驶汽车时代的到来。

英特尔:自主研发

在过去几年里,包括台积电、英特尔、三星、SK 海力士等晶圆代工厂和 IDM,相继大力投入 MRAM 研发。

EETimes 发布一份报告显示,英特尔自主研发的商用 MRAM(磁阻随机存取存储器) 已经做好大批量生产的准备。提交这篇论文的英特尔工程师 Ligiong Wei 表示:「英特尔嵌入式 MRAM 技术可在 200 摄氏度下实现长达 10 年的记忆期,并可在超过 100 万个开关周期内实现持久性。由于具有省电的特性,英特尔的嵌入式 MRAM 很有可能率先用在移动设备上,例如物联网 (IoT) 之类的设备商应用,通海还能搭上 5G 世代的列车。」

优势

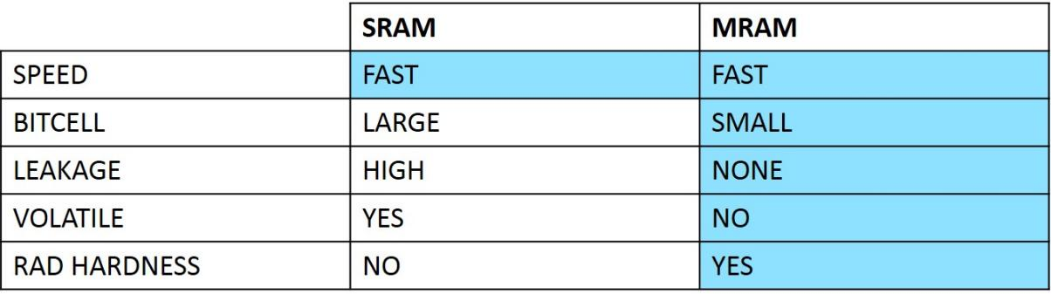

成本更低、能耗更低、非挥发性且抗辐射

片上系统 (SoC) 严重依赖 SRAM 技术来高速访问常用数据。SRAM 无处不在:可能每个 SoC、ASSP 和处理器都使用 SRAM,并且对于许多设备(尤其是处理器)来说,大部分芯片总面积可能被 SRAM 占据。

性能是 SRAM 的主要优势,但它是以牺牲芯片面积和功耗为代价的。与大多数其他类型的存储器相比,SRAM 存储器非常大:对于相同的位数,SRAM 比 DRAM 大 20-30 倍,可能比闪存大 100 倍以上。SRAM 的速度、灵活性以及与 CMOS 工艺的轻松集成带来了显著的芯片成本损失。

SRAM 的另一个弱点是漏电,这会导致待机功耗。对于电池供电的物联网 (IoT) 设备来说,高待机功耗可能是一个大问题,因为许多设备大部分时间都处于闲置状态。如果电池在闲置期间耗尽,电池寿命就会受到严重影响。考虑到这一点,SRAM 的性能是以高昂的成本为代价的。

此外,使用 SRAM 的嵌入式系统必须在系统进入睡眠状态时存储所有持久数据。代码和用于在启动时配置或个性化系统的数据也需要存储。闪存非易失性存储器 (NVM) 传统上担任此角色,但闪存技术具有显著的写入、读取和擦除限制,增加了系统的复杂性。

多年来,半导体行业一直在努力寻找一种可以取代 SRAM 并消除对 NVM 需求的存储技术;然而,直到最近,还没有找到合适的替代内存技术。许多候选人来了又走,受到费用、复杂性或许多其他问题的困扰,使他们不适合商业生产。然而,一种这样的替代技术即将在 SRAM 上取得进展:MRAM。

MRAM,即磁阻 RAM,是一种新兴的持久性存储器技术,已实现商业化生产。与 SRAM 和传统 NVM 相比,它具有以下主要优点:

与 SRAM 一样,它是可字节寻址的,但与 NVM 不同。

性能与 SRAM 相当,远高于 NVM。

MRAM 的耐用性可以与 SRAM 相匹配,而 SRAM 的耐用性比 NVM 高出许多数量级。

MRAM 没有与 NVM 相关的复杂缺点,例如扇区擦除和磨损均衡。

虽然这些特性使 MRAM 与 SRAM 更加接近,但 MRAM 与 SRAM 之间有四个关键特性:成本、漏电流、非易失性和抗辐射性。考虑到这四个因素,MRAM 抓住了 SRAM 和 NVM 技术的最佳特性,同时避免了很多缺点。

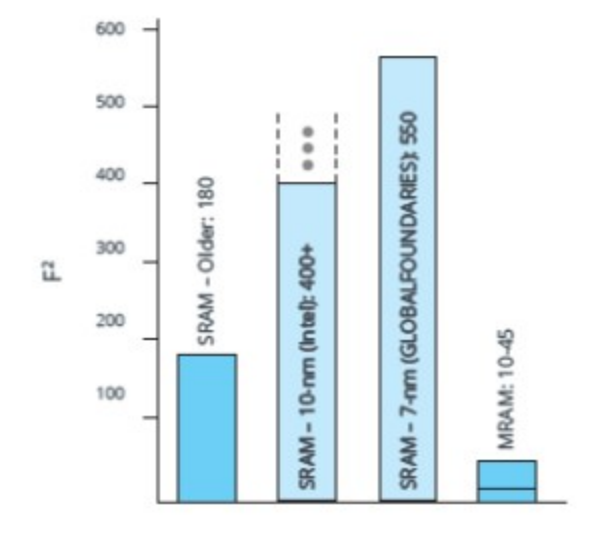

成本不到 SRAM 的一半

MRAM 块的大小约为等效 SRAM 块的三分之一。

无晶圆厂公司通常依赖其代工厂或专业内存供应商提供 SRAM 块,而代工厂会严格优化其 SRAM 位单元,将其视为关键知识产权。不根据所需的整体性能,而是特别根据该节点可用的 SRAM 技术来选择技术节点的情况并不罕见。如果 SRAM 要求规定了比电路其余部分要求更激进的节点(特别是不跨节点扩展的电路,例如模拟或高压电路),那么芯片成本可能会大幅上升。显示驱动器 IC 是这种现象的一个典型例子。

SRAM 的主要问题是位单元的大小——即使代工厂对其进行了高度优化。SRAM 位单元使用六到八个晶体管。甚至还有所谓的「非易失性 SRAM」单元需要 12 个晶体管,这使得它们超出了任何不惜任何代价对持久性有强烈需求的应用的成本范围。

随着技术节点的进步,SRAM 的大小问题越来越突出。

相比之下,MRAM 在其存储单元中使用单个晶体管。该晶体管与提供存储的磁阻结构相结合,因此存储器阵列内不需要其他支持晶体管。因此,包括外围电路在内的完整 MRAM 存储块的大小约为等效 SRAM 块的三分之一,或者小三分之二。这种关系在更先进的节点上会变得更加明显——也就是说,MRAM 的大小可能是 SRAM 的四分之一,在 10 纳米或更小的节点上甚至可能更小。

此特性的关键是磁阻元件,称为磁隧道结(或 MTJ)。与 SRAM(纯 CMOS)相比,它需要三个额外的处理步骤。这就形成了一种微妙的成本动态:这些额外的步骤使整体晶圆成本增加了 5-11%,但芯片尺寸的节省却非常可观,特别是对于大量使用 SRAM 的设计,以至于用 MRAM 替换 SRAM 会导致显著降低模具成本。

未来:MRAM 塑造人工智能和机器学习的未来

由于物理极限,半导体的制程微缩已经渐至瓶颈,经过多年发展的 DRAM 内存和 NAND 闪存已经难有潜力再挖。作为新兴技术的 MRAM 则拥有很多发展空间。除了英特尔,台积电在去年也传出有一重启 MRAM 产品的研发计划。

到目前为止,多种存储器介质被研究用于构建存算一体系统,包括基于电荷存储原理的传统存储器和基于电阻存储原理的新型存储器。传统存储器主要包括 SRAM、DRAM 和 Flash。其中 SRAM 和 DRAM 是易失性器件,频繁的刷新并不利于降低功耗。而 Flash 虽然是非易失性的,但是随着读写次数增加,浮栅氧化层会逐渐失效,反复读写可靠性很低。因此,各种基于电阻改变的新型存储器是实现存算一体的有效载体。

YoleDevelopment 分析称,到 2024 年,MRAM 的市场规模将增加 40 倍,制造工艺将减少到 16nm,存储容量则会从 1Gbit 增加到 8Gbit。2018 年至 2024 年间,MRAM 市场规模将以年均 85%的速度增长,到 2024 年将达到 17.8 亿美元。现在已经较为成熟的 eMRAM 在 2026 年市场规模将达到约 17 亿美元,相当于整个新兴 eNVM 市场的 76% 左右。

MRAM 在工业应用中也有广阔的前景,分析师表示,工业应用程序需要具有非常快的写入能力,且需要非易失性存储,但 NAND 闪存、NOR 闪存和 EEPROM 的写入速度都非常慢,并且消耗大量电力,而额外搭配电池的 SRAM,每隔几年就需要更换电池,对比之下 MRAM 更为合适。

随着汽车的电子化,对满足汽车恶劣驾驶环境、快速耐用的非易失性解决方案的需求正在逐渐增加。MRAM 具有近乎无限的耐久性及高可靠性,是能够满足电子应用程序中这种市场需求的非易失性存储器,最为理想。2022 年,瑞萨电子宣布推出 STT-MRAM 测试芯片,其表示,与采用 FEOL 制造的闪存相比,在 22nm 以下工艺中,采用 BEOL 制造的 MRAM 具有优势,因为它与现有 CMOS 兼容逻辑工艺技术,并且对额外掩模层的需求更小。

评论