日本佳能推出纳米压印半导体制造设备

佳能于 10 月 13 日宣布,已将 FPA-1200NZ2C 商业化,这是一种纳米压印半导体制造系统,利用纳米压印光刻(NIL)技术实现尖端半导体电路的形成,并于当天开始接受订单。

本文引用地址:http://www.amcfsurvey.com/article/202310/451605.htm

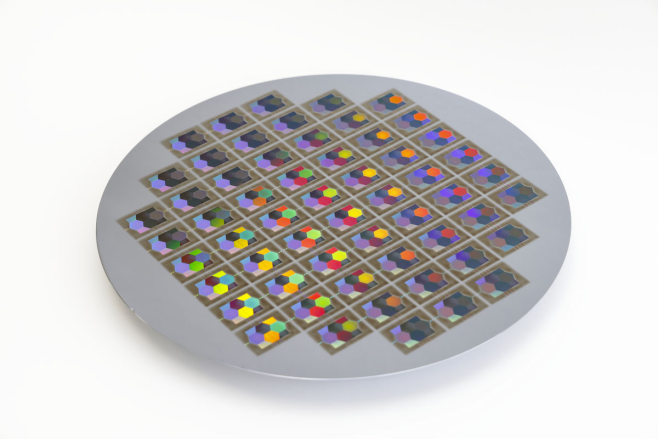

纳米压印半导体制造设备「FPA-1200NZ2C」

传统的投影曝光设备(例如 ArF 和 EUV)通过用穿过图案掩模的光照射晶圆上的抗蚀剂来形成电路图案,但使用 NIL 时,电路被印刷在掩模(模板)本身上。通过形成不规则形状并将它们像邮票一样压在抗蚀剂上。通过从母版创建副本,可以多次使用掩码,这具有降低设备成本的优点。

该公司的 NIL 技术起源于 2014 年收购的 Molecular Imprint 公司开发,2017 年将正在开发的「FPA-1200NZ2C」交付给东芝存储器(现在的铠侠)四日市工厂,并与该公司合作。一直致力于半导体器件的大规模生产。

新产品采用了新开发的环境控制技术,可抑制设备内细颗粒的污染。佳能表示,佳能的 NIL 技术可实现最小线宽 14 nm 的图案化,相当于生产目前最先进的逻辑半导体所需的 5 纳米节点。此外,随着掩模技术的进一步改进,NIL 有望实现最小线宽为 10nm 的电路图案,相当于 2nm 节点。

该设备采用紫外光作为光源,与传统曝光设备相比,占地面积更小,功耗更低。该公司表示,它将能够生产与尖端工艺兼容的逻辑/存储器,其功耗约为 EUV 曝光设备的 1/10。设备配置为每站配备一个压印头。标准规格为 2 站配置,但也可以变更为 4 站配置。吞吐量约为每小时 40 个掩模,因为需要将掩模通过抗蚀剂压到晶圆上,并且可以将多个设备聚集起来以提高吞吐量。叠印精度约为 4 纳米,叠印技术与传统投影曝光不同,采用逐芯片对准方法,对准要压印的每个镜头。该公司表示,通过改变激光的热分布,利用晶圆的热膨胀,能够高精度地纠正底层电路图案的变形。

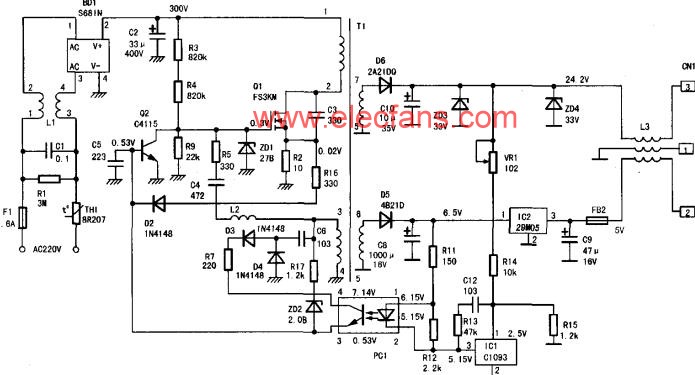

FPA-1200NZ2C 在工厂安装

此外,由于纳米压印技术不是一种制造半导体器件的技术,而是一种形成图案的技术,该公司表示,它有望得到广泛的应用,该公司表示,它还可以用于制造超透镜针对具有精细结构的 XR,该公司将在 10 月 19 日至 20 日在 Pacifico Yokohama 举办的私人活动「Canon EXPO 2023」上使用该技术。该公司计划展示使用该技术形成的超透镜技术。

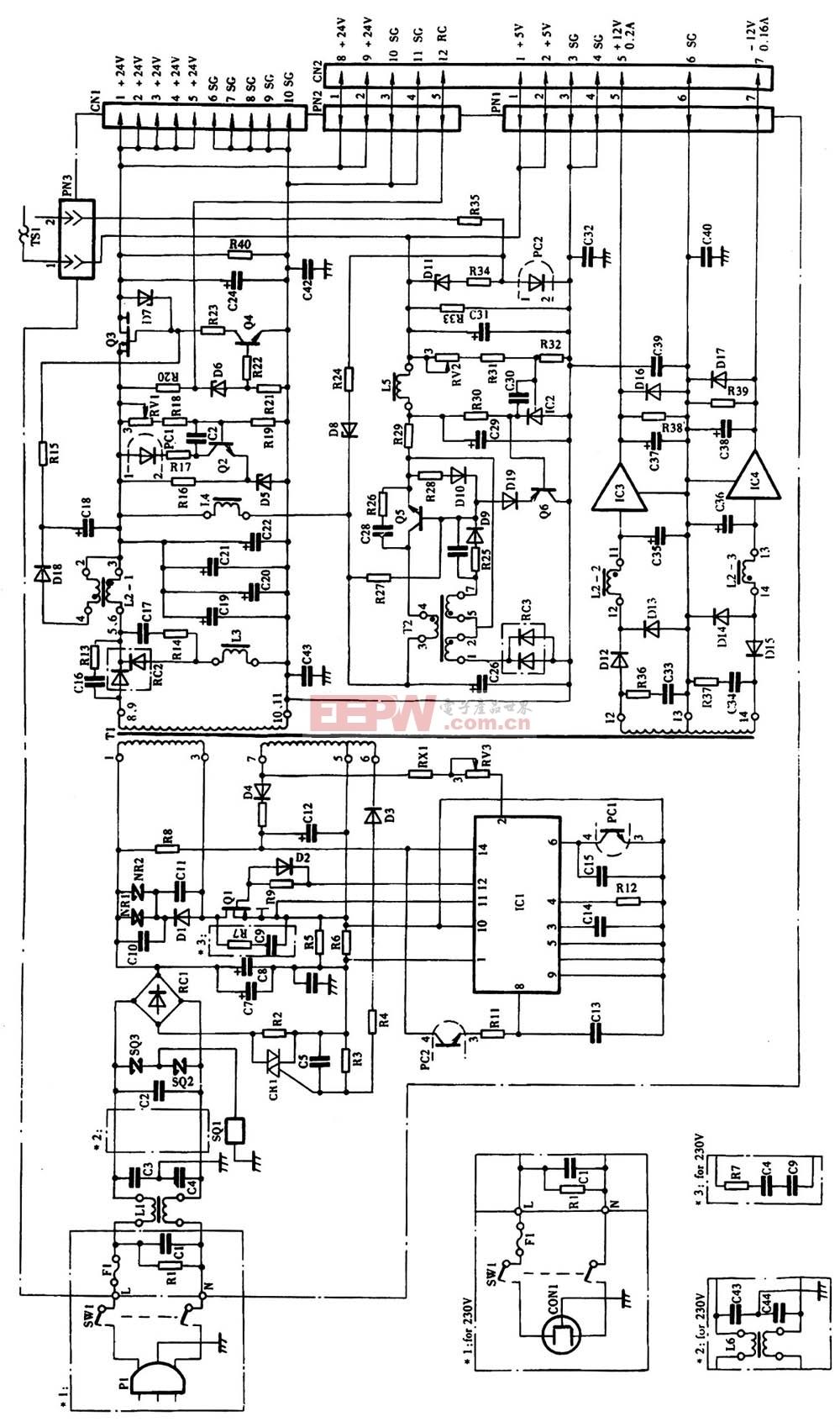

使用 NIL 形成的具有半导体以外的三维微结构的光学元件

纳米压印光刻技术是什么?

1995 年,华裔科学家周郁(Stephen Chou)教授首次提出纳米压印概念,从此揭开了纳米压印制造技术的研究序幕。纳米压印技术是当今最具前景的纳米制造技术之一,很可能成为未来微纳电子与光电子产业的基础技术。目前,纳米压印技术在国际半导体技术蓝图(ITRS)中被列为下一代 32nm、22nm 和 16nm 节点光刻技术的代表之一。国内外半导体设备制造商、材料商以及工艺商纷纷开始涉足这一领域,短短 25 年,已经取得很大进展。

纳米压印技术首先通过接触式压印完成图形的转移,相当于光学曝光技术中曝光和显影工艺过程,然后利用刻蚀传递工艺将结构转移到其他任何材料上。它就像盖章一样,把栅极长度只有几纳米的电路刻在印章上,再将印章盖在橡皮泥上,得到与印章相反的图案,经过脱模就能够得到一颗芯片。在行业中,这个章被称为模板,而橡皮泥则被称为纳米压印胶。

纳米压印技术将现代微电子加工工艺融合于印刷技术中,克服了光学曝光技术中光衍射现象造成的分辨率极限问题,展示了超高分辨率、高效率、低成本、适合工业化生产的独特优势,从发明至今,一直受到学术界和产业界的高度重视。因此,纳米压印技术被称为微纳加工领域中第三代最有前景的光刻技术之一。

纳米压印光刻不仅可以制造分辨率 5nm 以下的高分辨率图形,还拥有相对简单的工艺(相比光学曝光复杂的系统或电子束曝光复杂的电磁聚焦系统)、较高的产能(可大面积制造)、较低的成本(国际权威机构评估同制作水平的纳米压印比传统光学投影光刻至少低一个数量级)、较低的功耗、压印模板可重复使用等优势。

发展至今,相对成熟和普遍的纳米压印加工方式包括三类:热纳米压印、紫外纳米压印和微接触印刷(软刻蚀),其他新型工艺多为此三类工艺的改进版。其中,紫外纳米压印优势最为明显,是目前产业化最常见的方式,而微接触纳米压印则主要应用在生物化学领域。

评论