GAA技术才开始,半导体大厂已着手研发下一代CFET技术

外媒eNewsEurope报道,英特尔和台积电将在国际电子元件会议(IEDM)公布垂直堆叠式(CFET)场效晶体管进展,这有望使CFET成为十年内最可能接替全环绕栅极晶体管(GAA)的下一代先进制程。

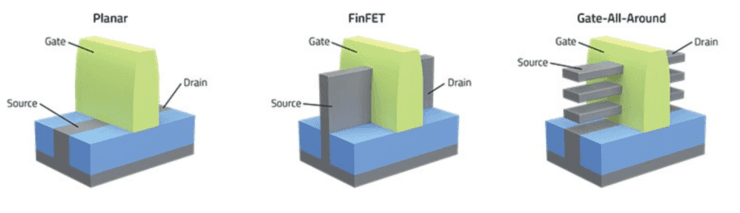

本文引用地址:http://www.amcfsurvey.com/article/202310/451192.htmCFET场效晶体管将n和p两种MOS元件堆叠在一起,以实现更高的密度。该项技术最初由比利时微电子研究中心(IMEC)于2018年所提出的。虽然,大多数早期研究以学术界为主,但英特尔和台积电等半导体企业现在已经开始这一领域的研发,借此积极探索这种下一代先进晶体管技术。

英特尔表示,研究员建构一个单片3DCFET,含三个n-FET纳米片,层叠在三个p-FET纳米片上,保持30纳米垂直间隙,英特尔公司在题为 "60纳米栅极间距的堆叠式CMOS逆变器演示(带电源通路和直接背面器件触点)"的演讲中将介绍利用60纳米栅极间距CFET的功能性逆变器测试电路。该技术还采用了垂直分层双电源漏外延和双金属栅极堆叠,并结合PowerVia背后供电等技术。

为了不被对手超越,台积电也会展示CFET技术。据悉,台积电客制逻辑芯片具有48纳米栅极间距,专注放在p型晶体管上的分层n型纳米片晶体管,拥有跨越六个等级的开关电流比。

台积电表示,CFET晶体管已证明耐用性超过90%,且成功通过测试。虽然台积电承认需要研究更多,才能充分利用CFET技术,但目前正在进行的工作是实现这一目标的关键一步。

评论