如何在有限空间里实现高性能?结合最低特定RDS(On)与表面贴装技术是个好方法!

SiC FET在共源共栅结构中结合硅基MOSFET和SiC JFET,带来最新宽带隙半导体技术的性能优势,以及成熟硅基功率器件的易用性。SiC FET现可采用表面贴装TOLL封装,由此增加了自动装配的便利性,同时减少了元件尺寸,并达成出色的热特性,在功率转换应用中实现了功率密度最大化和系统成本最小化。

本文引用地址:http://www.amcfsurvey.com/article/202309/450635.htm宽带隙(WBG)半导体开关,如碳化硅共源共栅结构FET(以下简称“SiC FET”)和SiC MOSFET的性能与其封装密切相关。在纯技术层面,纳秒级的开关速度和较低的比导通电阻带来非常低的损耗;在相同的芯片尺寸下,可以处理比硅基材料高得多的电流水平。然而,对外界的热阻实际上限制了实际功率转换电路中的结温,而且任何引线电感都会影响可达到的开关速度,因此器件制造商提供了不同的封装技术,以根据应用要求获得最佳性能。

图1:Qorvo SiC FET——硅基MOSFET和SiC JFET的“共源共栅”结构。

不同的封装适合不同的应用

为什么SiC FET的最佳封装取方式决于具体应用?带有大tab接点的传统通孔引线封装(如TO-247样式)可能极具吸引力;其允许在使用硅基MOSFET甚至IGBT的现有设计中向后兼容。事实上,SiC共源共栅结构FET的一个重要优势是它与旧技术的引脚兼容和栅极驱动相似性,这使得仅需对电路元件进行微小改动便能轻松升级,从而显著提升效率或功率等级。

TO-247器件的大焊盘面积也非常适合直接连接至散热器,以获得数十瓦的耗散和较低的结温上升幅度。然而,这种封装的缺点为体积大、由机械装配导致的较高人工成本,以及引线电感和电阻。因此,特别在高功率密度设计中,通常倾向于采用表面贴装技术(SMT)封装;它可以自动放置元器件并采用回流焊接,与PCB连接处的电阻及电感也实现最小化,接近于零。然而,此种方式可能会导致较低的排热效率;其散热路径通常通过电气终端进入PCB。这可能会限制大功率应用的运行,而这也正是WBG器件的优势所在。

基于封装方式的局限进行价值评估

PCB走线和封装引线的电感及杂散电容,会由于WBG器件的快速电压和电流边缘速率而产生瞬态电压和电流;例如,SiC具备超过100 kV/µs和1000 A/µs(图2)的能力,这有助于实现低开关损耗,特别是在“硬开关”功率转换拓扑结构中。

然而,依据我们十分熟悉的公式:V = -L di/dt,仅仅10nH或大约10mm的引线长度就会由于这个电流边缘速率而产生10V的尖峰。如果该引线为源极连接,且与栅极驱动回路共用,则会向栅极电路导入10V的电压,从而影响栅极去偏和抗噪能力,造成更高的功率损耗。同样,仅仅10pF的杂散电容与100 kV/µs的边缘速率,会根据I = C dV/dt的公式产生1安培位移电流;其不确定的回流路径还可能包括敏感信号连接。电容还会与杂散电感一并引发,可能造成电路不稳定和产生不良的EMI特征。

图2:采用Qorvo SiC FET所产生的电路边缘速率示例

当然,这些影响可以得到缓解;例如,通过使用开尔文连接到栅极驱动回路的源头、采用负关态电压,和通过细致的布局实践将电容与电感降至最低[1]。然而,残余的杂散值对于TO-247等引线封装来说仍然是个问题,因此通常会通过定制栅极驱动或使用阻尼器来有意减缓边缘速率,但代价是更高的开关损耗。

无引线封装,如PDFN型(无引线功率双平面),在很大程度上解决了杂散电感的问题;一些WBG器件制造商提供了这种封装,并强调其较小的尺寸和较低的轮廓/厚度,以适合高密度设计。与TO-247引线器件相比,由于热扩散不足,PDFN封装的结点到外壳的热阻(Rθ(J-C))要差10倍以上,由此限制了其在高功率下的应用。此外,由于器件和PCB间没有引线连接,无法吸收热膨胀不匹配产生的应力,热机械性能也会受到影响。

作为一种替代方案,D2PAK封装有时可用于WBG器件,并提供针对高电流的7引线版本,还可选择用于源的开尔文连接。然而,这种表面贴装封装仍存在“引线”;由于电阻和电感的存在,其Rθ(J-C)与最佳TO-247值相比相差3倍。当然,它确实在漏极与其它连接之间带来固有的宽物理间距优势,使其能够满足高电压下所推荐的爬电与间隙距离。

TOLL封装是一个很好的解决方案

如图3所示,使用TOLL封装(无引线TO,MO-229)可以让Rθ(J-C)低至0.1℃/W,接近理想状态;Qorvo SiC FET系列的UJ4SC075005L8S器件便是一个实例。这一低值通过先进的cell功能单元设计、银烧结裸片连接和晶圆减薄实现。TOLL封装的尺寸为10mm x 11.7mm,相比D2PAK小30%。漏极和其它连接间存在一个很大的空间,但由于引线比D2PAK短得多,因此寄生电感也低得多。此外,TOLL的高度为2.3mm,为D2PAK的一半,这为热机械设计中的散热器提供了额外的鳍片高度,同时在服务器电源装置(PSU)等空间受限的设计中保持了相同的整体外形尺寸。与相同应用中的D2PAK解决方案相比,这有可能进一步降低器件结温。因此,TOLL封装解决方案的热阻可能优于D2PAK,特别是在焊盘提供更大的裸片尺寸时。

图3:现可用于SiC FET的TOLL封装

在TOLL封装中,所有热传导均通过源极引脚和漏极焊盘连接实现;可以将之重新焊接至安装于PCB的铜焊盘上,以传导热量。当然,热量仍必须有所去处;可以在PCB的背面直接安装一个紧凑的可焊接SMT散热器,通过PCB的通孔进行热连接。由于完全消除了通孔封装和机械固定散热器的手动安装工作,并且FET和散热器均可以采用自动化装配进行安装,因此这种热机械设计大大节省了装配成本。该器件还可以被焊接至绝缘金属基板(IMS)上,以获得最终性能,并与尺寸更大的机械连接散热器集成。

参考文献1讨论了这类布局;文献还指出,一个长1.6mm、直径0.5mm、未填充、壁厚0.025mm的导热孔带来约100℃/W的热阻。一个由200个此类通孔组成的矩阵,可以很容易地布置在TOLL封装的tab接点下,并产生一个从漏极焊盘到底面铜地的大约0.5℃/W热阻。在许多应用中,这将提供非常有效的热耦合和最小的温差。

顶面冷却的SMT封装也在市场上迅速出现,并提供了更佳的性能。然而,工程师们需要一些时间来克服顶面冷却封装的相关挑战;其中包括将不同高度的多个器件装配至同一冷却面,同时还要管理整体设计中的爬电与间隙要求。

图4:在同一电压等级下,TOLL封装的不同器件实现的导通电阻

实现10倍于硅基MOSFET的额定峰值电流

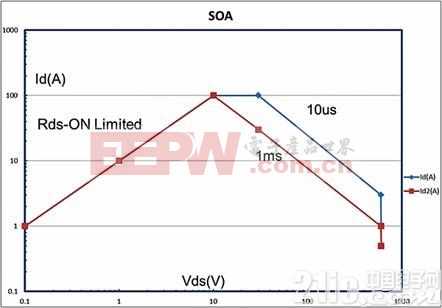

在TOLL封装的SiC FET中,异常低的封装热阻,以及由于超低5.4毫欧导通电阻和高达175℃的SiC FET结温而产生的低功率损耗,都使得其与其它开关相比具有较高的峰值电流承受能力并能承受更长的时间——即“I2t”性能。在功率转换电路中,负载可能会瞬间浪涌或短路,这就为器件在给定脉宽下所能承受的最大峰值电流提供了宝贵的额外安全裕度。当SiC FET用于固态断路器应用时,预计会出现高瞬态故障电流,因而必须在没有压力的情况下承受。图5显示了TOLL封装的SiC FET在达到安全工作极限前,承受给定峰值漏极电流的时间达到硅基MOSFET的10倍以上,由此提高了健壮度,让故障检测电路获得更长的反应时间,使其对电流尖峰的干扰性触发更具免疫力。

图5:峰值脉冲电流(I-t)电流能力比较——Qorvo TOLL封装的SiC FET和硅基MOSFET

应用

采用Qorvo TOLL封装的额定750V共源共栅结构SiC FET针对低静态和动态损耗进行了优化,展示了紧凑表面贴装开关的可行性。由此,这些系列器件的各种额定导通电阻在5-60毫欧之间,适合从几百瓦到数千瓦的相对高功率水平应用;包括AC/DC电源、电池充电器、电视和便携式充电站,以及替代能源、数据通信和一般工业应用中的功率转换。

在电路保护应用中,TOLL封装的SiC FET将在电动车充电器、电池关断电路,和建筑电气智能面板中找到用武之地——这些电气智能面板正变得更加智能,以提供动态负载管理。得益于Qorvo SiC FET的小尺寸/高性能指标,它们可以被考虑用于空间有限的终端应用。在此种情况下,与使用其它技术的高导通电阻器件相比,其需要更少的散热装置,并产生一个整体系统成本更低且功率密度更高的解决方案。当需要并联多个替代器件以实现与SiC FET相同的电气和热性能时,情况更是如此——后者将产生额外的器件成本,以及处理和安置的费用。

结论

一个宽带隙半导体功率开关的优劣取决于其封装。现在,共源共栅结构SiC FET有了TOLL版本,可以利用其低损耗来进一步提升系统功率密度。

利用Qorvo基于网络的FET-Jet计算器探索其技术优势,请访问:

https://info.unitedsic.com/fet-jet

参考资料

[1]《基于SiC FET应用的实用PCB布局考虑》,Qorvo

作者:Pete Losee 来源:Qorvo

评论