3nm工艺意味着什么?

联发科已经宣布推出首款 3nm 工艺芯片,这是一款未命名的旗舰产品天玑 SoC,预计将于 2024 年进入量产,这个消息意义重大。让我们先解释一下 3nm 工艺芯片是什么,以及它对您的实际性能和电池寿命意味着什么。

本文引用地址:http://www.amcfsurvey.com/article/202309/450633.htm什么是 3nm 工艺芯片?

在半导体处理器的早期,只需测量晶体管栅极长度,从最初几十年的微米(百万分之一米或微米)开始,逐渐发展到纳米。随着技术的成熟,晶体管尺寸的减小,我们看到了性能的提高、功耗的降低以及发热量的降低。当时,可以简单的说,较小的晶体管比较大的晶体管更好,并且制造商之间的工艺节点代际改进是相似的。

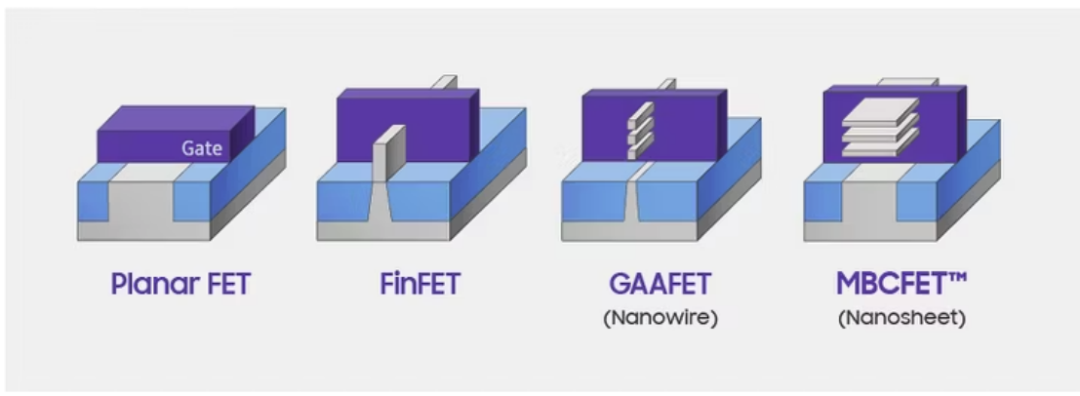

然而,在过去的几十年里,随着集成电路设计(从平面晶体管到各种类型的 3D 晶体管)和制造工艺的各种专有改进,仅根据晶体管尺寸来衡量性能增益变得更加复杂。因此,3nm 工艺芯片本质上是一个营销术语,与晶体管的尺寸没有直接关系。由同一制造商制造的两代工艺节点(例如 5nm 和 3nm)的芯片在较小的工艺节点上应该具有较小的整体晶体管尺寸。但是,这些大小不一定对应于流程节点名称。

相反,微芯片制造商按照现已失效的国际半导体技术路线图 (ITRS) 以及后来的国际设备和系统路线图 (IRDS) 制定的处理器节点扩展计划,通过工艺节点名称来营销其每一代处理器路线图中,例如 5nm 工艺和 3nm 工艺节点。这些芯片预计将遵循 IRDS 对接触栅极间距和金属间距等尺寸的预测,但可能具有更小的尺寸。

来源:三星

因此,比较英特尔的 5 纳米工艺芯片和 AMD 的 5 纳米工艺芯片可能不像查看晶体管栅极长度(或金属间距等其他指标)那么简单。对于新工艺节点命名法有多种提案,例如 GMT(建立晶体管密度)和 LMC(包括存储器和互连密度)提案。同时,最好比较竞争芯片的实际性能或比较同一制造商的不同代工艺节点之间的性能。

在这种情况下,也是工艺节点名称与制造商工艺差异的一个很好的例子,联发科宣布它已经使用台积电的 3nm 工艺开发了首款芯片。台积电和联发科都没有更准确地说明正在使用的是台积电专有的 3nm 工艺节点,是 N3、N3E、N3S、N3P 还是 N3X。联发科的新闻稿称:「联发科首款采用台积电 3nm 工艺的旗舰芯片组预计将于 2024 年下半年开始赋能智能手机、平板电脑、智能汽车和各种其他设备。」考虑到该日期,它很可能是 N3S 或 N3P 流程。

相反,与台积电的 N5 工艺(属于 5 纳米工艺节点的一部分)相比,这些公司详细介绍了各代改进。据称,台积电的 3nm 工艺与 N5 工艺相比「目前在相同功率下速度提高了 18%,或者在相同速度下功率降低了 32%,逻辑密度增加了约 60%」。

有哪些公司在使用 3nm 工艺芯片?

到目前为止,除了联发科之外,苹果也已经宣布了 3nm 芯片。需要注意的是,三星作为代工厂已经在生产 3nm 工艺芯片,但还没有移动芯片——它们目前正被加密货币机器使用。

高通使用台积电和三星作为其代工厂,目前尚不确定其尚未公布的 3nm 工艺移动芯片将使用这两家公司中的哪一家。

正如我们提到的,苹果在 9 月 12 日的活动中为 iPhone 15 Pro 和 iPhone 15 Ultra 机型推出基于 3nm 工艺的 Apple A17 SoC。该公司在 2023 年成为市场上第一家拥有 3nm 工艺芯片的智能手机/平板电脑制造商。多年来,苹果已经放弃了三星作为其 A 系列处理器的制造商,转而选择台积电。

在 GeekBench 测试中, 苹果 A17 Pro 多核跑分达到了 7199, 虽然比其 A16 的 6989 提升不大, 但依然遥遥领先于骁龙 8 Gen 2 领先版。在单核跑分方面, 苹果 A17 Pro 3.77GHz 的主频发威, 不仅相比 A16 有了明显提升, 甚至超越了苹果 M2 Ultra 芯片。即使面对 Intel 的酷睿 i9 14900KF 变态的 6GHz, 单核性能仅落后 12% 左右。

据报道,苹果已预订了台积电 2023 年 90% 的 3nm 工艺产能,据说这将扩展到预计为 Mac BookPro 和 iPad Pro 系列提供支持的 Apple M3 芯片。然而,最近的报道表明 MacBook Pro M3 和 iPad Pro M3 要到明年才会推出。

3nm 工艺芯片对您意味着什么?

平均而言,较小的晶体管可提供改进的性能、功耗和散热。晶体管密度也随着晶体管的减小而增加。因此,由于晶体管内和晶体管之间的行进距离更小,电子在电路内行进的时间更少,从而提高了处理速度。它们还需要更少的能量来移动这些较短的距离,从而减少所需的输入功率,最后,由于移动较少,导致以热量形式损失的能量更少。

所有这些都意味着更好的性能、电池寿命和周围的加热。这意味着采用 3nm 芯片的设备将比采用同一芯片制造商的 5nm 或 4nm 工艺芯片的设备速度更快、使用寿命更长。

当然,影响这些指标的因素不仅仅是所使用的处理器或 SoC。芯片设计或架构、与其配对的内存的速度以及包括软件在内的其他因素决定了终端设备(无论是智能手机、平板电脑还是个人电脑)的性能。

电池寿命还受到设备上其他组件(例如显示屏)的功耗以及硬件和软件优化的影响。最后,散热在很大程度上取决于设备的设计以及与之相结合的冷却量。

事实上,最新一代工艺节点芯片的生产成本将更高,并且在生产初期每片晶圆的产量比前几代芯片更低,这也意味着它们将仅限于生产的高端手机和平板电脑。因此,预计 3nm 工艺芯片智能手机和平板电脑将在至少一年内仅在各制造商的旗舰产品中提供。苹果只会为 iPhone Pro 机型引入 3nm 工艺 A17 SoC 的传言呼应了这样的产品开发决定。

处理器扩展解释

让我们从基础知识开始:半导体是具有导体和绝缘体特性的非金属材料。单晶硅是最常用的半导体材料,通过「掺杂」或添加其他元素的杂质来提高其电荷携带特性,可以提高其导电性。生长这种材料或基板的薄晶圆,并在其上通过各种物理和化学过程绘制或构建电路。

现代半导体处理器由数十亿个晶体管构成,这些晶体管构成了集成电路的元件以及其他组件。这些晶体管放大或调节电路内的电信号流,重要的是还可以充当开关,形成逻辑处理器和存储器的基础。在半导体处理器制造历史的大部分时间里,用于制造芯片的工艺节点的名称是由晶体管栅极长度的最小特征尺寸(以纳米为单位)或最小线宽来指定的。350nm 工艺节点就是一个例子。

让我们正确地看待这一点——纳米是十亿分之一米。随着集成电路设计和半导体制造技术的不断进步,在晶圆上构建越来越多的晶体管成为可能,在几十年内从数千到数百万,然后数十亿。不过,工艺节点命名法并未遵循线性路径,3D 晶体管的出现使问题变得更加复杂。用于描述工艺节点的纳米数不再必然与晶体管的任何物理尺寸相关,例如栅极长度、金属节距或栅极节距。

相反,制造商遵循既定的 IRDS 路线图,在处理器扩展方面实现连续几代的进步,该路线图本身基于晶体管密度每 18-24 个月翻一番的摩尔定律。

总而言之,「3nm 工艺芯片」中的「3nm 工艺」是指用于构建芯片的技术的世代。3nm 是芯片制造商使用的营销术语,而不是对芯片技术规格(如性能或尺寸)的描述。然而,与同一制造商的 5nm 工艺芯片相比,3nm 工艺芯片的晶体管更小。随着晶体管变得更小,我们可以预期性能和能效会提高。

评论