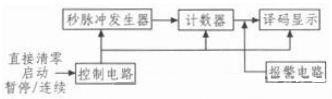

555定时器数字秒表电路

本文介绍了一个数字秒表电路的原理、设计和操作。数字秒表可以是一个显示以分、时、秒为单位的实际时间的电路,也可以是一个显示时钟脉冲数的电路。这里我们设计的是第二种类型,其中电路显示从0到59的计数,代表60秒的时间间隔。换句话说,这里的电路只显示秒数的时间。这是一个简单的电路,包括一个555定时器来产生时钟脉冲和两个计数器IC来进行计数操作。

本文引用地址:http://www.amcfsurvey.com/article/202305/446450.htm数字秒表电路原理:

这个电路是基于同步级联的2级计数器工作原理。其想法是显示时钟脉冲从0到59的计数,代表60秒的时间间隔。这是通过使用一个以星形模式连接的555定时器IC来产生每个间隔为1秒的时钟脉冲来实现的。当第一个计数器从0到9计数时,第二个计数器在第一个计数器的计数值达到9时开始计数操作。计数器IC以级联的形式连接,每个计数器的输出连接到BCD-7段解码器,用于驱动7段显示器。

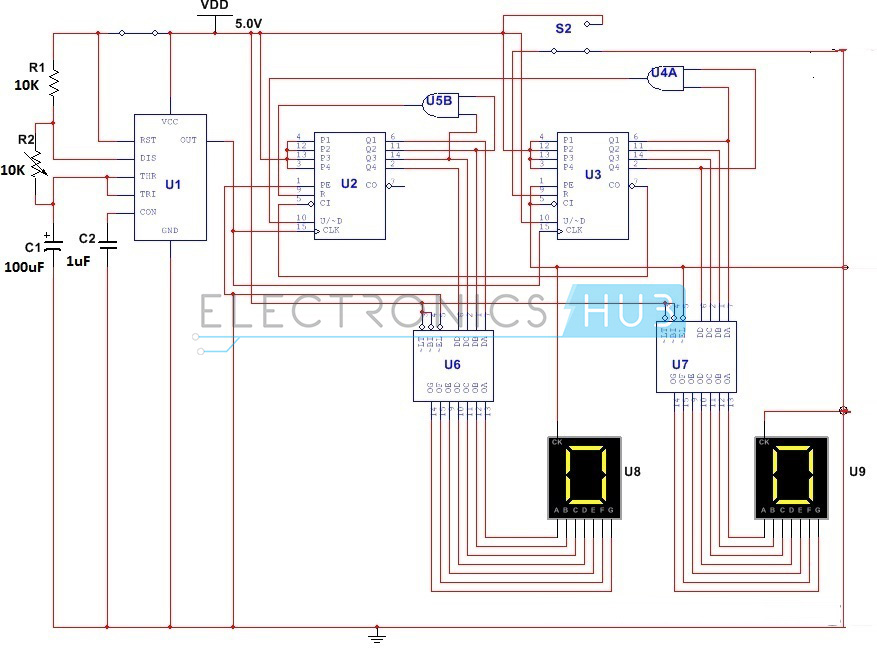

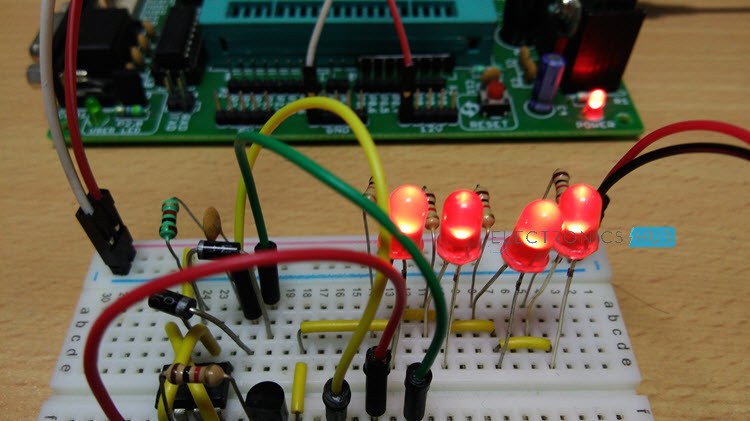

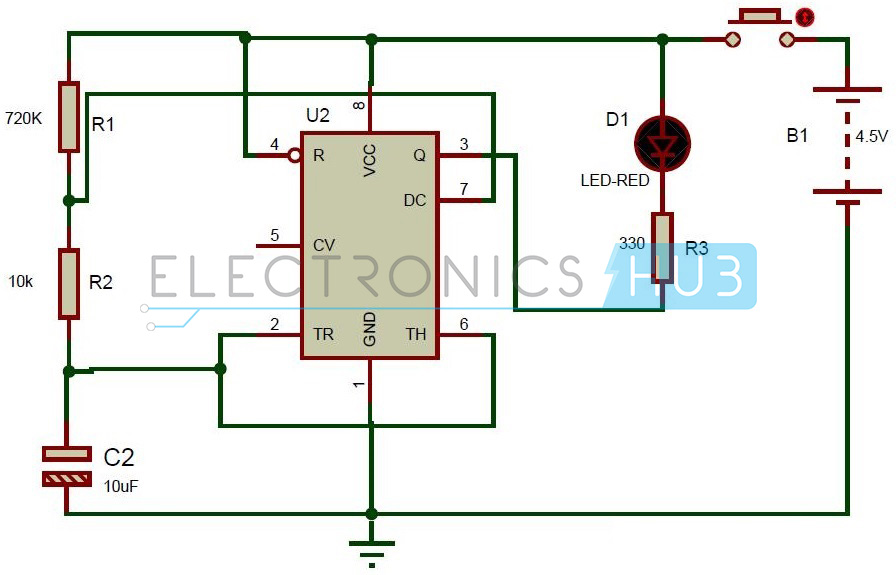

数字秒表电路图:

数字停表的电路图

数字秒表电路设计:

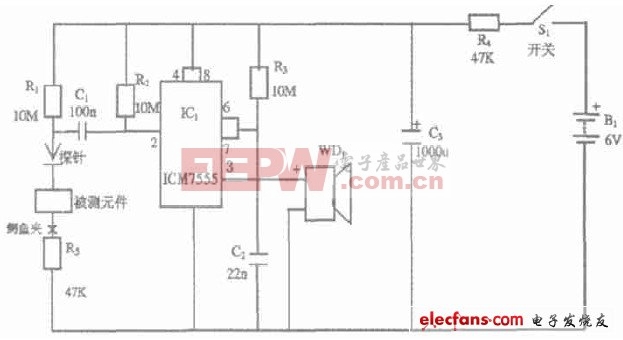

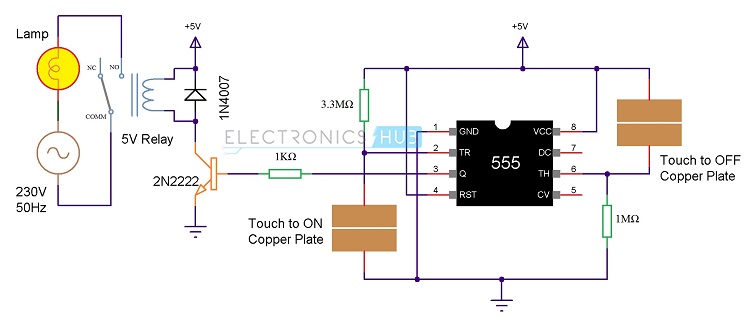

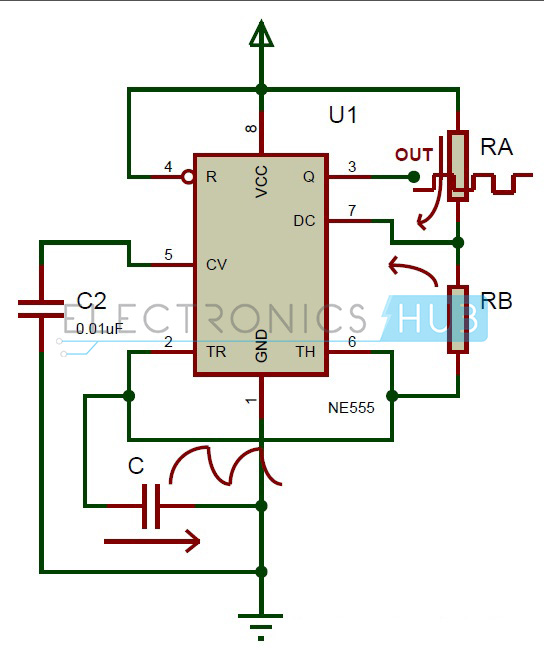

设计的第一部分涉及到设计555定时器的星形多谐振荡器安排。这里需要的时间周期是1秒。输出信号的频率由f = 1.44/ (Ra+Rb) C给出,我们可以计算出C的值,假设Ra和Rb的值约为10K。这里我们得到一个100uF的电解质电容。

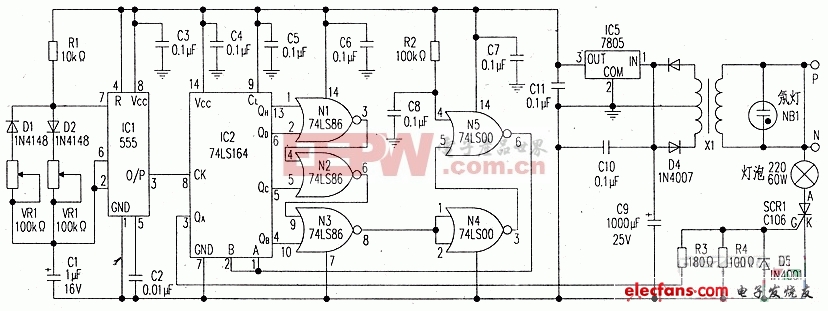

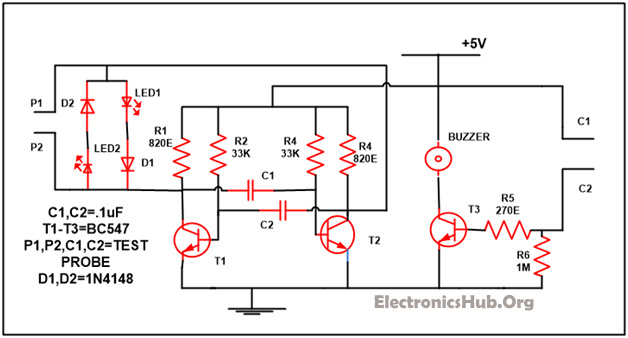

设计的第二部分涉及到将两个计数器IC-4510以同步级联的方式连接起来。这是通过将计数器IC的时钟引脚连接到555定时器的输出来实现的,从而形成平行的时钟输入信号。其中一个IC的输出引脚被连接到另一个IC的输入引脚。

由于我们关心的是,一旦第一个计数器达到9的计数值,就启动第二个计数器,我们通过设计一个简单的组合逻辑电路来实现。回顾一下计数器的真值表,对于一个9的时钟脉冲计数,相应的二进制计数或计数器输出信号的状态是1001。换句话说,当计数为9时,Q1和Q4处于高逻辑信号。在这里我们使用一个AND门IC 7408,它的输入连接到第一个计数器的Q1和Q4引脚,输出连接到第二个计数器的U/D引脚。

在这里,我们的要求是显示时钟脉冲,直到数到60。这可以通过确保第二个计数器在计数达到5的时候复位来实现。我们通过设计一个简单的逻辑电路来实现,该电路由另一个AND门IC组成,其输入端连接到第二个计数器的Q3和Q2引脚。

第三部分是设计显示电路。这是通过将每个计数器IC的输出连接到BCD到7段解码器的输入来完成的。每个解码器ICs 4511的输出被连接到7段显示器。

数字秒表电路的工作:

一旦常开开关转到关闭位置,电路就开始工作。定时器555以频繁的间隔产生高低信号,从而产生振荡信号,其频率是基于两个电阻和充电电容的值。换句话说,定时器555集成电路产生所需时间周期的时钟脉冲。这个时钟信号被送入两级排列的BCD计数器CD4510。CD4510由四个同步时钟的D-触发器组成,它们被连接在一起以实现计数操作。时钟脉冲由两级同步级联排列的两个CD4510计数器进行计数。当集成电路U3收到时钟脉冲时,它开始从0到9计数。一旦计数达到9,AND门IC U4A产生一个高逻辑输出,该输出被送入IC U2的U/D引脚。IC U2开始进行计数操作。IC U2继续其计数操作,每当U3达到其结束计数时,IC U3也继续计数。然而,一旦IC U2的计数达到6,复位引脚被AND门U5B设置为高电平。该计数显示在由BCD到7段解码器CD4511驱动的7段显示器上。因此,该电路显示从0到60的时钟脉冲。

数字秒表的应用:

这个电路可以作为问答比赛的指示器使用。

数字秒表的局限性:

该电路不显示实际时间,而是显示时钟脉冲的计数。

由于传播延迟,使用数字计数器IC在整个操作过程中会产生一个时间延迟。

这是一个理论上的电路,可能需要修改。

评论