使用NCP1623A设计紧凑高效的PFC级的IC控制电路设计

之前我们介绍过快速设计由 NCP1623 驱动的 CrM/DCM PFC 级的关键步骤中的定义关键规格与功率级设计。本文将详细说明IC控制电路设计中的细节:FB引脚电路、VCTRL 引脚电路、CS/ZCD 引脚电路、CSZCD电阻器设计等内容。

本文引用地址:http://www.amcfsurvey.com/article/202304/445952.htm步骤 3:IC 控制电路设计

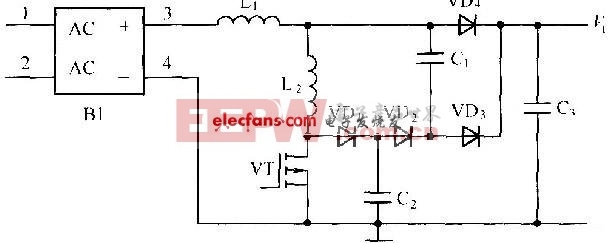

如图 1 所示,反馈配置包括:

● 一个电阻分压器,用于降低体电压,以向 FB 引脚提供反馈信号。出于安全考虑,分压器的上层电阻通常由两个或三个电阻构成。否则,RFB1 的任何意外短接都会将输出高电压施加到控制器上并将其破坏。

● 一个滤波电容器,通常置于 FB 引脚与接地之间,以防开关噪声令反馈信号失真。通常使用的是 1−nF 电容。一般来说,与线路电阻相比,它与反馈电阻形成的极点必须保持在非常高的频率上。实际上,

(公式18)

通常会得到较好的结果。

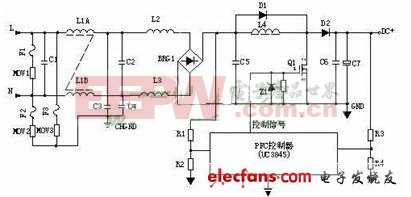

图 1:系统板的电路图

● 一个 2 型补偿网络。该电路由两个电容和一个电阻构成,用于设置交越频率和环路特性。

A 版本 (NCP1623A) 具有输入电压跟随升压(follower boost)功能。该技术涉及到降低输出电压,以优化 PFC 级效率并显著压缩其尺寸和成本。特别地,它可以显著降低升压电感和 MOSFET 损耗。由于输出电压必须要高于线路电压,因此只有在低压下输出电压才会降低,而在高压条件下,输出电压将调节至默认标称电压(Vout,nom 通常设置为 400V 左右)。实际上,NCP1623A 通过反馈引脚控制这一 2 级输入电压跟随升压(follower boost)操作,而反馈引脚会拉动仅在低压下启用的电流 IFB(LL)(通常为 25 μA)。

如数据表中所述,这将产生以下调节电压:

● 高压线输出电压 Vout,HL = Vout,nom:

(公式19)

● 低压线输出电压 Vout,LL:

(公式20)

根据应用中高低压线的输出电压规格,反馈电阻值可通过下式获得:

● 上层反馈电阻 RFB1

(公式21)

● 下层反馈电阻 RFB2

(公式22)

选择RFB1和RFB2后,FB引脚的相关功能在我们的应用中将定义如下:

● 反馈电阻比 KFB:

(公式23)

● 输入电压跟随升压(follower boost)失调电压 VOFF(LL):

![]()

(公式24)

● 高压下的 DRE 进入/退出 VOUT :

![]()

(公式25)

进入:2.5 · 95.5% · 157 ≈ 375 V

退出:2.5 · 97.5% · 157 ≈ 383 V

● 低压下的 DRE 进入/退出 VOUT :

![]()

(公式26)

进入:2.5 · 95.5% · 157 − 140 ≈ 235 V

退出:2.5 · 97.5% · 157 − 140 ≈ 243 V

● 高压下的 SOVP 进入/退出 VOUT :

![]()

(公式27)

进入:2.5 V · 105% · 157 ≈ 412 V

退出:2.5 V · 103% · 157 ≈ 404 V

● 低压下的 SOVP 进入/退出 VOUT :

(公式28)

进入:2.5 V · 110% · 157 − 140 ≈ 292 V

退出:2.5 V · 108% · 157 − 140 ≈ 284 V

● 高压下的 FOVP 进入/退出 VOUT :

![]()

(公式29)

进入:2.5 V · 107% · 157 ≈ 420 V

● 低压下的 FOVP 进入/退出 VOUT :

(公式30)

进入:2.5 V · 114% · 157 − 140 ≈ 307 V

退出:2.5 V · 112% · 157 − 140 ≈ 300 V

● 高压下的 UVP 进入/退出 VOUT :

![]()

(公式31)

进入:0.3 V · 157 ≈ 47 V

● 低压下的 UVP 进入/退出 VOUT :

![]()

(公式32)

进入:1.2 V · 157 − 140 ≈ 48 V

退出:1.3 V · 157− 140 ≈ 64 V

VCTRL引脚电路

为了找到“控制到输出”传递函数,输出电压将用输出电流和输出阻抗的乘积来定义。使用公式 2 并假设效率为 100%,输出电流由下式给出:

(公式33)

基于以下公式,输出电压与输出电流的偏微分等效于输出负载电阻 Rload:

(公式34)

因此,输出阻抗中可以包括 δiout / δvout,而总输出阻抗为:

(公式35)

控制电压与输出电流的偏微分为:

(公式36)

因此,“控制到输出”传递函数的定义如下:

(公式37)

其中,在 A 版本中,Ton.max 在低压下为 12.5 μs,在高压下为 5 μs,而 G0 为静态增益。

通过 FB 电阻网络比、OTA 跨导和 VCTRL 补偿网络获得“输出到控制”传递函数,如下所示:

(公式38)

其中 ictrl 是 OTA 输出电流,而 zctrl(s) 是 VCTRL 补偿电路阻抗。

OTA 输出电流定义如下:

(公式39)

其中 GEA 是 OTA 跨导增益,而 Vout 是直流输出电压。

使用公式 38 和公式 39,“控制到输出”传递函数可通过下式获得:

(公式40)

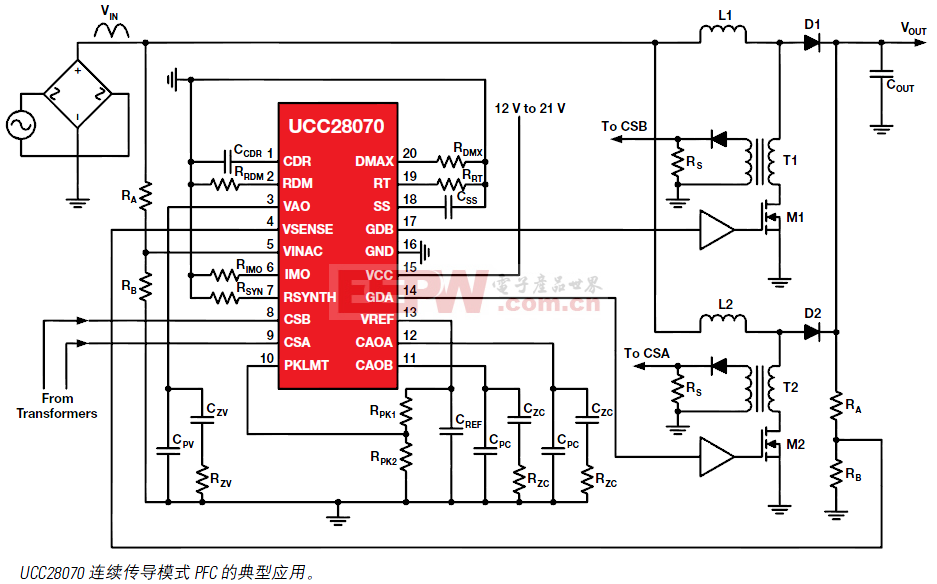

其中 R0 = Vout / (VREF · GEA),而补偿网络电路是 CZ、RZ 和 CP ( << CZ ),如图 2 所示。

图 2:FB 和 VCTRL 电路

公式 37 中的极点和公式 40 中的零点位置相近,交越频率 fC 位于公式 40 中零点和第二极点之间。相位裕量 m(弧度)由 CP 调整。由此,我们得到以下公式:

● 反馈零电容 CZ:

(公式41)

● 反馈零电阻 RZ:

(公式42)

● 反馈极点电容 CP:

(公式43)

负载电阻 Rload 通过下式计算:

(公式44)

交越频率 fC 应高于 PFC 升压级极点 fP:

(公式45)

最高交越频率的条件是相位裕量的最坏情况,其中线路电压为高值,以增大“控制到输出”传递函数的带宽。如果应用中的目标是 25−Hz 的交越频率和 60° 的相位裕量(π/3 弧度),则采用的是:

(公式46)

CS/ZCD引脚电路

如果电流检测电阻两端的电压超过 0.5 V,电路就会检测到过流情况。因此:

(公式47)

将公式 6 中的结果合并,得到:

(公式48)

在实际情况中,将选择 0.12Ω 电阻以保持一定的裕量。RSENSE 损耗可使用公式 10 进行计算(用 RSENSE 取代 RDS(on)),由此得到 MOSFET 导通损耗:

(公式49)

可以看到,0.12Ω 的电流检测电阻在满载、低压条件下将消耗约 124 mW。

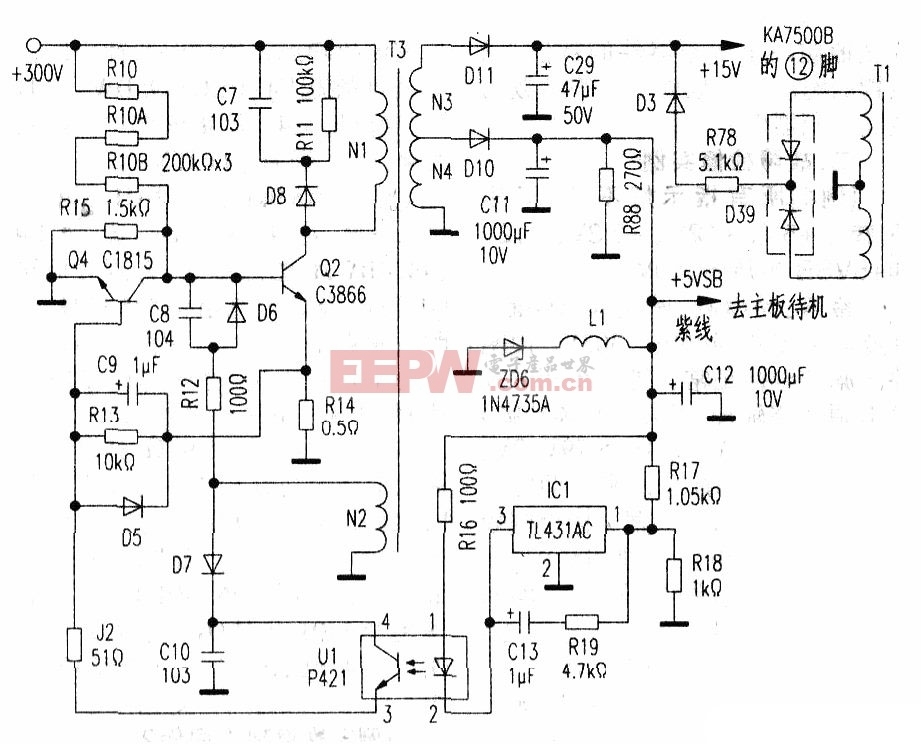

图 3:ZCD 漏极感测

基于漏极感测的 ZCD 电路如图 3 所示。漏电压由 CS 电阻网络进行感测,并由 KCS 按比例降低:

(公式50)

其中 KCS 为 133,而 RCS2 一般为 22 k。

RCS1 和 RCS2的值必须选择高值,以免在待机期间的功耗过高。在待机期间没有开关,RCS1 与 RCS2 串联的电压为恒定电压,等于 Vmains,rms · √2。待机功耗由下式给出:

(公式51)

NCP1623 在 CS/ZCD 引脚上集成了前沿消隐,从而免除了滤波电容器。CS/ZCD 电路中不允许有电容器,因为这会造成 CS/ZCD 信号失真,从而导致错误或无法进行 ZCD 检测。使用示波器探针来探测 CS/ZCD 信号时必须要小心,因为示波器探针通常会增加 10−pF 的电容。

在升压转换器中,升压电感器一个引脚的平均漏电压等于升压电感器另一个引脚上的 Vin 电压,这是因为:如果忽略电感器的串联电阻,电感器两端的平均电压降在伏秒平衡中为零伏特。因此,要计算 VCS/ZCD 的平均值来获得输入电压信息。

平均 VCS/ZCD、VSNS 被用在 ZCD、线路检测、OVP2(仅限 C 版本)和掉电检测(在 A 和 C 版本中禁用)中,如下所示:

● 线路检测阈值:

(公式52)

(公式53)

● OVP2 阈值(仅限 C 版本):

(公式54)

● 掉电阈值(在 A 和 C 版本中禁用):

(公式55)

(公式56)

图 4:辅助ZCD 绕组感测

可以使用图 4 所示的电路图来生成 CS/ZCD 引脚的信号。借助辅助绕组电压电容 CAUX、 RAUX 和 DAUX,可以在 DAUX 的阴极生成一个电压,其大小为功率 MOSFET 漏电压乘以辅助 (NAUX) 与初级 (NPRI) 变压器匝数比之积。之前所述的参数 KCS 现在定义如下:

(公式57)

其中 KCS 为 133,NPRI/NAUX 为 10,而 RCS2 一般为 62 kΩ。

通过这种方法可以传递较低的电压,并且低 RCS1 值也降低了对寄生电容的灵敏度。

该电路的另一个优点是在待机期间没有电流消耗(没有开关活动,因此也就没有 Vaux 电压)。

必须提请注意的是,激活了掉电功能的产品版本无法使用此电路。当功率 MOSFET 漏电压用于 ZCD 时,其他所有情况均与所述的完全相同。

CSZCD电阻器设计指南

当 RCS电阻桥在漏极感测电路(如图 3)处的总电阻位于 M 范围内时,它对低至几百 fF 的寄生电容非常敏感。寄生电容可以是从 RCS电阻器节点到 GND 或功率 MOSFET 漏极。这些寄生电容效应可导致永久性错误故障检测事件:OCP、OVS 或 OVP2 的触发,从而使控制器无法正常运行。

避免寄生电容效应的一种简单方法是减小电阻器的值,同时让分频比 KCS保持在 133 左右。降低 CS/ZCD 桥电阻值 (RCS1 + RCS2 ) 是以高待机功耗为代价的。

如果图 3 中的 RCS1a + RCS1b + RCS1c 应高于 5M,建议在漏极侧设置一个 500−V SMD 高值电阻器(如 RCS1a = 5.1 M),并串联两个低值 200−V SMT 电阻器(如 RCS1b = RCS1c= 240 k)。这是为了避免连接到 GND 的电阻器间电容在 FET 导通周期之前难以放电。根据经验,不建议使用 3 个等值电阻器来平衡漏电压。

测试台上的实验已证明,SMD1206 和 0805 在寄生电容方面要优于槽孔电阻器。

RCS1 和 RCS2 必须尽可能靠近 CS/ZCD 引脚。连接 RCS 电阻器的 PCB 走线必须尽可能短,且走线的宽度要尽可能小(最小寄生电容)。最好在 RCS 电阻器和 DRV、VIN、VDRAIN 铜走线之间保持 1 cm 的安全距离,以避免耦合。

布局和抗扰度注意事项

NCP1623 对噪声不是特别敏感。

不过,常规的电源设计布局规则还是适用的。提请注意以下几点:

● 必须最大程度降低功率传输回路的环路面积。

● 电源接地(用于提供电流回路路径)的星形配置。

● 电路接地的星形配置。

● 电路接地和电源接地应通过一条单独的路径进行连接,不允许有环路。

● 该路径最好满足以下条件:在非常靠近电流检测电阻 (RSENSE) 的接地端子的位置将电路接地连接到电源接地。

● 应在电路 VCC 和 GND 引脚之间放置一个 100 或 220−nF 的电容,并确保连接长度最小。

● RCS 电阻器必须尽可能靠近 CS/ZCD 引脚,且必须避免与 GND 或任何其他信号有电容耦合。

● 建议在 FB 引脚上放置一个滤波电容器,以保护引脚免受周围噪声的影响。不过,该电容必须要很小,不能让 FB 引脚检测到的电压出现失真。

总结

表 1:主要公式

表 1.主要公式(续)

图 5:100W 设计的系统电路图

评论