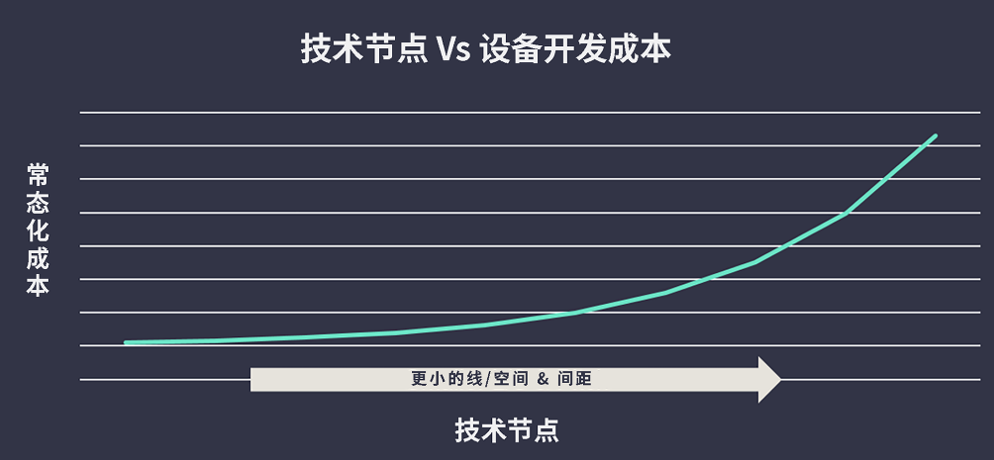

异构集成推动面板制程设备(驱动器)的改变

l 对系统级封装(SiP)的需求将基板设计推向更小的特征(类似于扇出型面板级封装FO-PLP)

本文引用地址:http://www.amcfsurvey.com/article/202304/445465.html 需求趋同使得面板级制程系统的研发成本得以共享

晶体管微缩成本的不断提升,促使行业寻找创新方法,更新迭代提升芯片和系统的性能。正因此,异构集成已成为封装技术最新的转折点。

异构集成将单独制造的部件集成一个更高级别的组合,该组合总体上具有更强的功能、更好的操作特性,以及更低的成本。这种更高级别的组合称为系统级封装 (SiP)。异构集成最初是在高性能计算设备上进行,这些设备通常被用于机器学习和人工智能应用。

系统级封装设计

提高性能指的是将逻辑和存储器更紧密地结合在一起,达到比嵌于主机板上的单个芯片能实现的更高的带宽连接。为了提高速度和带宽,行业正在探索系统级封装 (SiP) 设计。

l 系统级封装是将两个或更多的集成电路封装在一起,系统芯片 (SoC) 则是将这些芯片的功能集成在单个晶片上。

l 系统级封装设计持续发展,以尽可能紧密地包含更多功能。

l 当今一些最先进的设备中,单个封装就含有几十个芯片,晶体管数量超过一万亿。

该图表显示了系统级封装设计的选项。图表显示,为了满足对异构集成的需求,需要新的类似于系统级封装的封装技术出现,以实现高效的性能并加快上市时间。

为了将逻辑和存储器更紧密地结合在一起,半导体行业正在将系统级封装设计转移到集成电路基板。与标准印制电路板相比,它能实现更小的特征、更紧密的间距和更高的输入/输出(I/O)量。这些因素导致基板上的设计规则与扇出型晶圆级封装 (FO-WLP) 和扇出型面板级封装 (FO-PLP) 的设计规则更加相像。

l 扇出型是一种新兴技术,可以使芯片被附着在更大尺寸的圆形、正方形或矩形基板上。使用大尺寸的基板可以使每个区域容纳更多的芯片,从而降低单位成本。

l FO-PLP在300/330mm的圆形尺寸上进行封装,相比FOWLP更具成本优势。

但是,小批量研发FO-PLP技术的成本不断增加却是一个巨大的障碍。

研发挑战

FO-PLP 市场的主要驱动力是成本(而非性能)。这个市场面临的挑战是需要在更大的尺寸(从 300 mm 圆形晶圆到 600 x 600 mm 正方形面板)上满足晶圆级规格和产量。

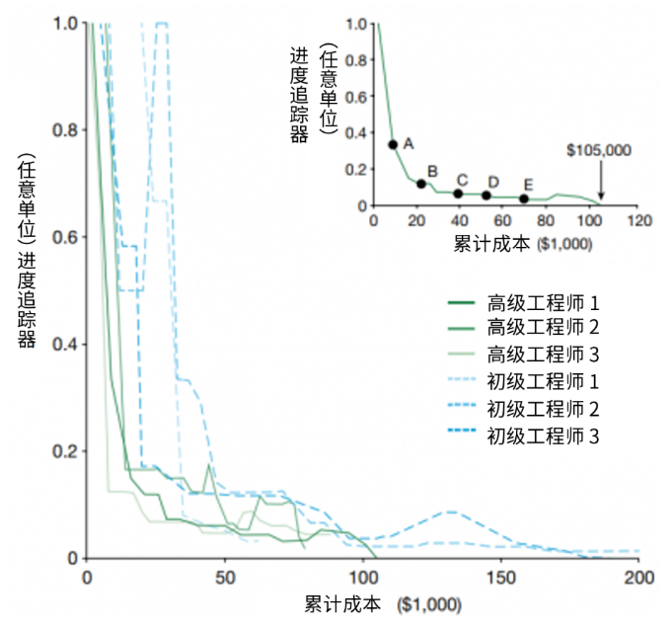

这些面板的市场很小,导致整个供应链没有足够高水平的研发投资来解决处理大型面板相关的关键问题。

l 由于投资不足,FO-PLP的产量水平较低,不足以获得转移到更大基板尺寸的经济效益。

l结果是,大多数扇出型业务都停留在晶圆上。

技术融合

类似的面板 (510 x 515 mm) 被用于基板市场,这一市场预计在未来四年都会面临数量上的显著增加,尤其是在最具技术挑战性的领域。

由于基板和 FO-PLP 要求(例如特征尺寸和均匀性)的技术融合迫在眉睫,我们很可能可以使用相同或相似的平台来应对这两个市场。融合可以实现更强大的设备供应商基础。

通过将面板标准化为几种尺寸并采用现有的接口和设备标准,我们可以增加通用系统平台的数量。标准化将有助于降低面板级制程系统的研发成本。

l 产量增加将有助于将成本分摊在新的设备上。这可以加大规模,实现一个强劲的面板制程设备市场。

随着面板产量接近晶圆级封装的水平,预计将有更多的应用从晶圆转移到面板,以利用预期的成本优势。

l Micro-LED 或“封装天线”解决方案等相邻市场也有望推动面板产量的提升。更高的产量将更有可能实现成本的降低,从而有助于提高面板级解决方案的竞争力。

SEMSYSCO 提供湿法制程设备(例如图中的 CUPID),它能处理大至600 x 600 mm的基板

多米诺骨牌效应

随着产量提升,相信将会产生多米诺骨牌效应,成本降低将推动产量提升和研发投资增加。这些投资将有助于推动更有效的自动化、更多的机器学习和智能、更高的可靠性和更少的缺陷。所有这些都将导致成本降低,从而继续推动面板业务量的增加。

泛林集团一直致力于推动半导体行业的创新。通过此前对 SEMSYSCO的收购我们正在投资面板级制程市场,并处于创新的前沿。

评论