氮化镓GaN驱动器的PCB设计策略概要

NCP51820 是一款 650 V、高速、半桥驱动器,能够以高达 200 V/ns 的 dV/dt 速率驱动氮化镓(以下简称“GaN”) 功率开关。只有合理设计能够支持这种功率开关转换的印刷电路板 (PCB) ,才能实现实现高电压、高频率、快速dV/dt边沿速率开关的全部性能优势。本文将简单介绍NCP51820及利用 NCP51820 设计高性能 GaN 半桥栅极驱动电路的 PCB 设计要点。

NCP51820 是一款全功能专用驱动器,为充分发挥高电子迁移率晶体管 (HEMT) GaNFET 的开关性能而设计。与击穿电压额定值相似的硅器件相比,制造 GaNFET 所使用的芯片尺寸更小。因此,哪怕与同类最佳的硅 MOSFET 相比,GaNFET 的栅极电荷、输出电容和动态导通电阻也大大降低。此外,GaNFET 没有 PN结,因此漏极-源极上没有本征寄生体二极管,也就没有与第三象限操作相关的反向恢复电荷。

GaNFET 非常适用于离线半桥功率拓扑、无桥 PFC 和单端有源箝位拓扑。这些功率级常常采用零电压开关 (ZVS),但也可以在硬开关条件下采用大约 400V 的电压工作。所有这些改进使得 GaNFET 能够以 MHz 范围或接近该范围的频率开关,漏源边沿速率高达 100V/ns。能否实现基于 GaN 的功率级的最优性能,在很大程度上取决于设计人员对寄生电路元件(如封装电感、PCB 走线电感、变压器电容)以及元器件选择和布局的理解。虽然硅 MOSFET 功率系统中也存在这些寄生元件,但在 GaN 功率解决方案中,当受到其中存在的高 dV/dt 和 di/dt 激励时,会有更明显的响应,因此会产生问题。

NCP51820 的 MLP 无引线功率封装(图 3)以及行业中的各种无引线 GaNFET 功率封装(图 1 和图 2),体现了为充分降低寄生电感所作的设计努力。同样,必须特别注意 PCB 设计和元器件布局。为了充分发挥利用 NCP51820 驱动高速半桥功率拓扑中使用的 GaN 功率开关的优势,有一些重要的 PCB 设计因素需要考虑,本白皮书将重点讨论其中的一些重要注意事项。

HEMT GaN 和 NCP51820 封装说明

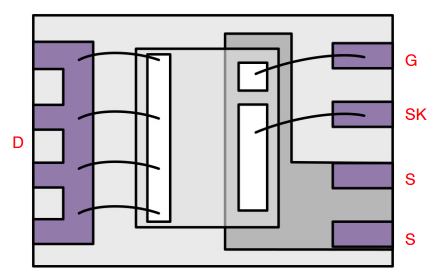

大多数 GaNFET 封装包含一个专用源极开尔文返回引脚,如图 1 中的“SK”所示,其作用只是为了将栅极驱动返回电流送回 NCP51820。较高电流的漏源引脚通过多条焊线焊接到多个焊盘,不过为了简明起见,图 1 中的简化示意图仅显示了一条焊线连接。NCP51820 输出和 GaNFET 栅源开尔文引脚之间的接口必须是直接单点连接,该接口特别重要,如含有源极开尔文引脚的 GaNFET 部分所述。

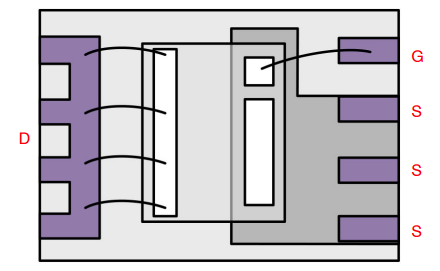

但是,并非所有 GaNFET 都包含一个专用源极开尔文返回引脚,例如图 2 所示的示例。对于不含源极开尔文返回引脚的 GaNFET,为 PCB 设计中的栅极驱动部分布线时必须特别注意。对于半桥功率级的开关节点连接,高压侧 GaNFET 的源极直接连接到低压侧 GaNFET 的漏极,构成一个承载高 di/dt 负载电流的高 dV/dt 节点。不建议直接使用此高压开关节点的栅极驱动返回引脚,如不含源极开尔文引脚的 GaNFET 部分所述。

图1. 含有源极开尔文返回引脚的典型 GaN

图2. 不含源极开尔文返回引脚的典型 GaN

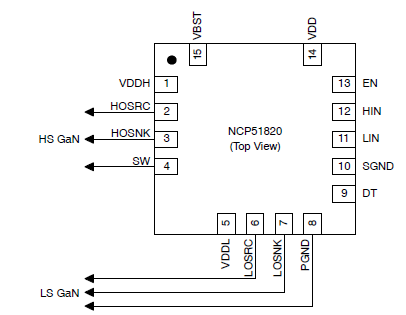

NCP51820 采用 4x4 mm 无引线封装,所有逻辑电平输入和编程功能都设置在 IC 右侧,与策略性设置在 IC 其余三侧的电源功能分开。基于设计策略安置引脚,以便必要时提供高压隔离。以下 PCB 布局部分说明,将充分展现 NCP51820 引脚分配的优势。

图3. NCP51820 GaN 驱动器引脚分配

PCB 设计策略概要

使用 GaNFET 开始 PCB 设计时,最好根据优先级考虑整个布局,如下所列。

1. 必须采用多层PCB设计,并且按照本文所述适当使用接地/返回平面。高频率、高电压、高dV/dt和高di/dt都要求采用多层PCB设计方法。为了实现基于GaN的功率级的全部优势,接地平面必须采取适当的布线或设计,而廉价的单层PCB设计无法做到。

2. 开始时,首先将对噪声最敏感的元器件安置在 NCP51820 附近。VDD、VDDH 和 VDDL 旁路电容以及 VBST 电容、电阻和二极管应尽可能靠近各自的引脚。

3. 将 DT 电阻直接放在 DT 和 SGND 引脚之间。

4. HO和LO、拉电流和灌电流栅极驱动电阻应尽可能靠近 GaNFET。

5. 将 NCP51820 和关联的元器件移到尽可能靠近 GaNFET 拉电流和灌电流电阻的位置。

6. 如果可能,安置 GaNFET 时使 HO 和 LO 栅极驱动长度尽可能匹配。为了避免高电流和高 dV/dt 流经过孔,两个 GaNFET 最好和 NCP51820 位于 PCB 的同一面。

7. 应将 HO 和 LO 栅极驱动视为两个独立的、相互电隔离的栅极驱动电路。因此,HO 和 LO 各自都需要专用铜触点 (copper land) 返回平面,这些平面在第 2 层上,位于第 1 层栅极驱动布线正下方。

电源环路、开关节点、栅极驱动环路的正确布线以及使用平面,对于顺利完成 GaN PCB 设计至关重要。这部分内容如有需求,后续可能会推送新的文章配合插图对每一项加以说明。对于栅极驱动器,正确的布线和噪声隔离将有助于减少额外的寄生环路电感、噪声注入、振铃、栅极振荡和意外导通。目的是设计一个精心考虑了适当接地,同时让受控电流以最小环路距离流经直接通路连接的高频电源 PCB。

元器件布局和布线

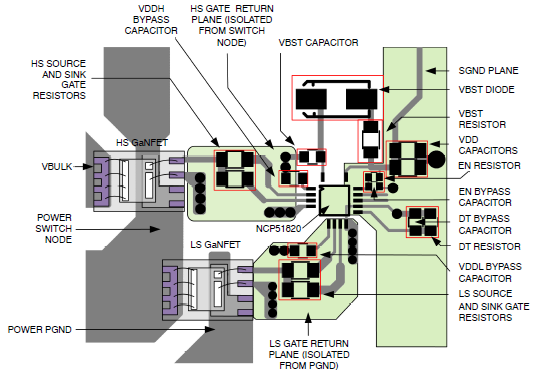

图 4 突出显示了 NCP51820 周围的关键元器件布局以及与 HS 和 LS GaNFET 的接口。

图4. NCP51820 元器件布局

含有源极开尔文引脚的GaNFET

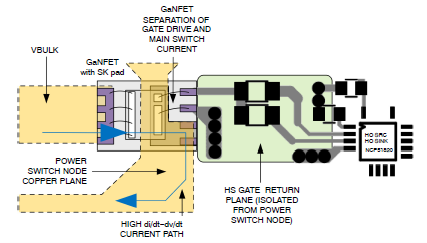

许多 GaNFET 封装包括一个专用源极开尔文引脚,用于将栅极驱动返回电流与功率开关节点(高压侧)或电源地(低压侧)出现的较高电流和电压电平隔离。对于具有专用源极开尔文引脚的 GaNFET,栅极驱动布线相当简单。推荐 PCB 布线设计示例如图 5 所示,可以看到高压侧 GaNFET 栅极驱动返回电流与功率开关节点电流有效分隔。

图5. 源极开尔文 GaNFET 布线

不含源极开尔文引脚的GaNFET

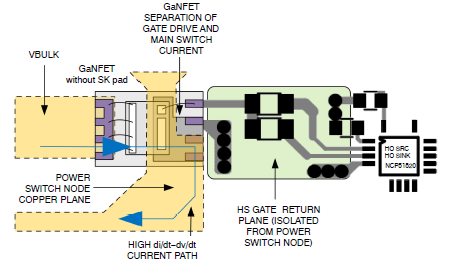

有些 GaNFET 封装不含专用源极开尔文引脚,还必须要仔细考虑,将栅极驱动返回电流与功率开关节点(高压侧)或电源地(低压侧)出现的较高电流和电压电平隔离。对于没有专用源极开尔文引脚的 GaNFET,应从 GaNFET 源极接出一段额外的铜蚀刻线,其唯一作用是将栅极驱动返回电流送回 NCP51820。尽管不如专用开尔文引脚连接那么有效,但这种布线技术仍然可以在栅极驱动电流和功率开关节点之间实现可接受程度的分离。推荐 PCB 布线设计示例如图 6 所示,可以看到高压侧 GaNFET 栅极驱动返回电流与功率开关节点电流有效分隔。无论何种类型的 GaNFET 封装,其设计目标都是避免 NCP51820 和支持电路接触到流过功率级的潜在破坏性开关电压和电流。

图6. 无源极开尔文引脚的 GaNFET 布线

评论