数据通信的“指挥官”!

数据通信快速发展,相关应用迅速普及,为满足海量的数据吞吐需求,改善传输延时,通信系统和数据中心的传输速度和处理能力变得至关重要。时钟芯片作为这些高性能通信系统和数据中心中必不可少的核心芯片,其性能及可靠性将直接影响系统的误码率和稳定性。

本文引用地址:http://www.amcfsurvey.com/article/202212/441386.htm5G通信与时钟同步

5G基站设备相比于4G基站,设备的功耗和传输容量增加,基站站点的配套设备需要进行相应的升级扩容。通过采用多载波聚合和大规模天线阵列等技术来实现高速率、低延时。它汇聚了多频点协同传输数据和多天线通道同步收发数据等技术,而这些技术都对时钟有高度严格的同步要求。

矽力杰最新推出SQ82201 是一款10路输出的高性能时钟发生器,集成模拟锁相环,具有强大的频率合成、抖动滤除、超低时延等功能。广泛应用于5G AAU,小基站,通信系统,服务器等。有效满足各类通信设备的时钟同步需求。

矽力杰时钟发生器方案

SQ82201 是一款10路输出的高性能时钟发生器,其中包括3路LVPECL差分输出和7路单端输出。SQ82201内部集成低噪声鉴相器(PFD),电荷泵(CP),环路滤波器,低相位噪声高频压控振荡器(VCO)和输出整数分频器。

SQ82201

高性能10路输出时钟发生器

● 7路单端LVCMOS输出:

○ 一个单端LVCMOS的33.33 MHz CPU时钟

○ 六路单端LVCMOS输出用于参考时钟缓冲

● 3路差分LVPECL输出对

● 可选择的外部晶体或单端输入参考源

● 为25MHz并联谐振晶体设计的晶振接口

● 156.25MHz输出, RMS相位抖动: <0.15ps (12kHz~20MHz)

● 电源噪声抑制PSRR: -80dBc

● 电源电压: 3.3V

● 紧凑型封装: QFN6×6-40

● 工作温度: -40~85°C

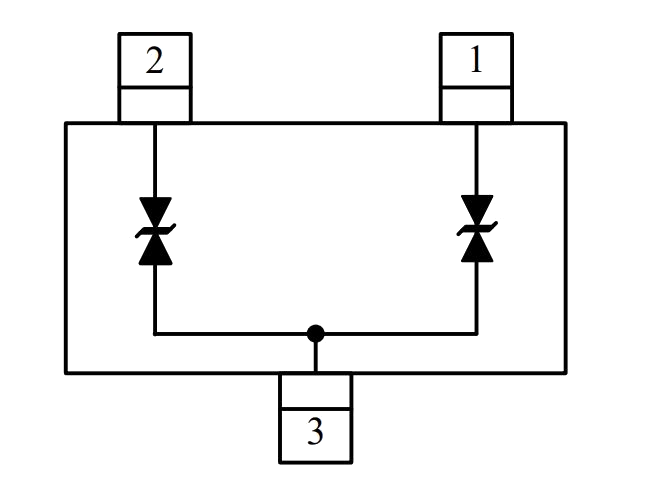

如图为SQ82201系统框图,SQ82201能够通过硬件管脚选择本地无源晶振或者外部参考时钟。同时也支持通过硬件管脚选择输出频点组合以及输出使能。

传统的系统设计中,各个数字芯片需要的工作时钟信号频率各不相同。在设计中采用多个独立的晶振时钟源给各个数字芯片提供时钟信号,往往会造成系统成本高,电路板面积大,设计复杂,且会产生各芯片间时钟无法同步的问题,给系统设计带来额外的开销。

当系统采用SQ82201时钟发生器,即可通过其中的高性能高频VCO锁定输入选定的参考时钟。同时产品内部集成整数分频器,可实现输出多路频率各不相同的高性能时钟,满足系统多个芯片的时钟频点和性能需求。高集成度的时钟发生器,能够进一步缩小芯片及外围电路尺寸,有助于满足现有和未来的基站通信的设计需求。

应用场景

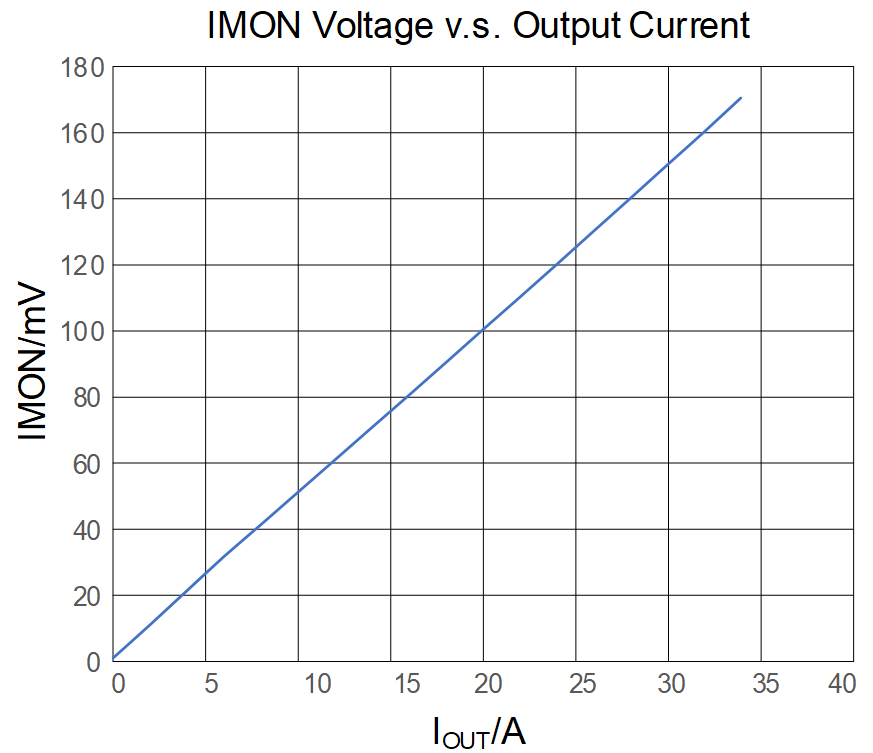

在衡量时钟信号质量时经常会提到抖动和相位噪声,二者分别从时域和频域的维度表征时钟信号短期频率稳定度。

SQ82201差分输出抖动分别如下所示:

156.25MHz: 109fs (12kHz~20MHz)

100MHz: 116fs (12KHz~20MHz)

目前主流的数据通信系统中,由于各个系统的数据速率、收发通道时钟恢复电路的带宽不同,对于链路时钟抖动的要求和积分带宽会略有不同。

SQ82201优越的抖动性能,符合当前所有主流通信系统时钟抖动的要求,为客户提供高集成度,极简外围电路的时钟发生器解决方案,有效满足5G通信等应用领域的时钟同步需求。

来源:矽力杰

评论