光芯片&电芯片共封装技术的主要方式

本文主要介绍了硅光芯片和电芯片共封装的几种不同形式及其主要特点。

本文引用地址:http://www.amcfsurvey.com/article/202212/441261.htm到 2022 年,全球互联网流量预计将达到每月近 400 EB,对数据中心互连带宽的需求将继续以指数级的速度增长 。预测到了2030年,数据中心能耗持续增长,全球数据中心的用电量超过 3 PWh,最坏的情况可能高达 8 PWh 。为了满足互联网流量需求,数据中心节点带宽需要达到 10 Tb/s ,为了减缓数据中心能耗增长的趋势,必须想办法降低系统、器件的功耗。每个封装的 I/O 引脚数差不多每6年翻一番超过I/O总带宽3、4年翻一番。解决这些速率差异需要3、4年 I/O 的带宽翻倍。

将硅光技术引入的目的是增加 I/O 带宽并最大限度地降低能耗。光集成电路(PIC)和电集成电路(EIC)如何封装,非常重要。光具有的最小信号衰减、低能耗、高带宽以及利用成熟CMOS生态系统的能力。反过来,这些因素直接影响到 I/O 带宽和能耗,因此,光与电的不当集成会抵消硅光子的所有潜在优势。下面将重点介绍 PIC 和 EIC 之间的集成方案。

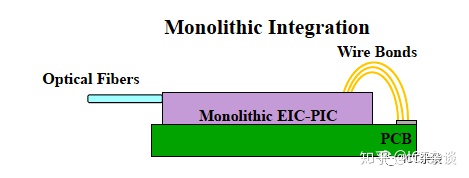

1、单片集成

图1 单片集成

单片集成是EIC和PIC加工在一块芯片上,在PIC 和 EIC 之间互连时无需额外的引线或bumps,从而最大限度地减少了由于封装而导致阻抗不匹配情况。通过将两个die组合成一个,封装简单。I/O 到计算节点可以通过wire-bonds或Flip-Chip到PCB。理论上,该封装是非常好的,但实际并非如此,硅光工艺节点相对电芯片工艺而言,比较落后。为单片集成开发的最先进工艺是45 nm和 32 nm制程,与电芯片10 nm 和以下工艺相比,这些工艺在性能上非常落后。此外,还存在高波导损耗、低光电二极管响应率和低光电二极管带宽的问题。总之,采用单片集成模式,目前来看,工艺制程的融合势必会牺牲一部分整体性能,而且单片集成开发成本非常昂贵,由此产生的技术不如异构集成开发灵活。

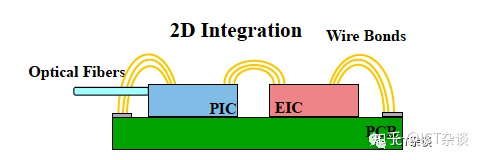

2、2D集成封装

图2 2D集成

2D集成是PIC 和 EIC 并排放置在PCB,如图2所示。通过引线进行互连以及和PCB之间的连接。2D 集成的好处是易于封装,但其最大的缺点是对引线的依赖。虽然引线可以达到 25 μm ,但 PIC 和 EIC 之间的连接仅限于单边,严重限制了 I/O数量。

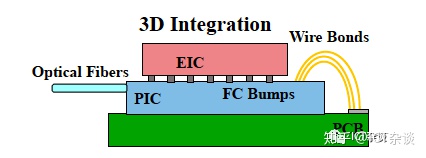

3、3D集成封装

图3 3D集成封装

3D封装也可最大限度的减小封装尺寸。在3D集成封装中,最常见的是将EIC倒装在PIC之上,如图3所示。EIC通过铜柱或者ubumps和PIC互连,然后再通过Wire Bonds与PCB进行互连。铜柱或ubumps互连间距范围为 40 μm ~50 μm,可以实现密集I/O。后续预计可以降低到20μm,10μm,甚至更小,满足更高密度的需求。3D 集成封装最大的问题在于散热。虽然 3D 集成可以提供更密集I/O间距和最小封装尺寸,但当前并没有最佳的散热方案。EIC产生的热量会传递到PIC上,每0.5W的功耗,都可能引起20℃的温升。对于PIC这种热敏感元件而言,这是致命的问题。如图4所示,3D集成还有另外一个方案,硅光芯片同时作为一个interposer中介层,里面有TSV,通过TSV直接和PCB形成互连。

图4 3D集成封装的另外一种模式

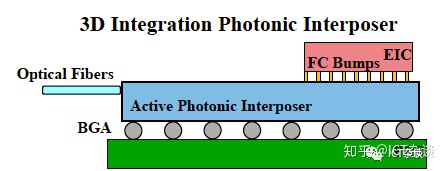

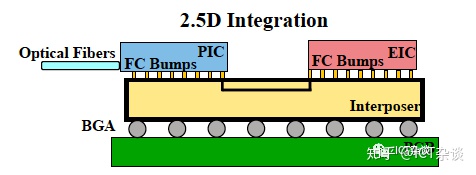

4、2.5D集成封装

图5 2.5D集成封装

2.5D集成封装,是一个折中的技术,EIC和PIC均倒装在interposer中介层上。2.5D 集成时,其封装尺寸大于3D集成,因为两个芯片之间是平面放置的,当然该模式也不限于这两个芯片的封装。同时,因为信号必须通过两次bumps,信号性能会一些影响。

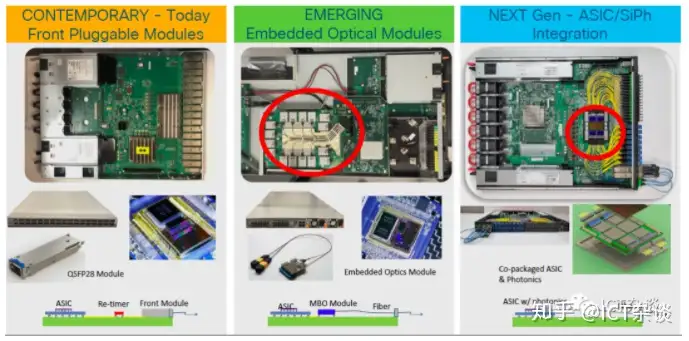

总结:如下图所示,光芯片和电芯片之间共封装技术是下一代技术的重点研究方向。然而,不同的封装形式,有着不用的优劣,2.5D、3D封装在不同厂家都有研究,功耗、互连性能都对何种封装形式有巨大影响。距离该技术的全面商用,预计还有几年,在这几年中,硅光技术、封装技术、散热技术等的发展都将影响最终的实际结果。让我拭目以待吧。

评论