「芯调查」Chiplet“乐高化”开启 UCIe联盟要打造芯片的DIY时代

Chiplet(小芯片或芯粒)虽然受到工业界和学术界的追捧,之前只是“少数人的游戏”。但随着UCIe产业联盟的诞生,一切将成为过往。一个由顶级厂商所主导的Chiplet生态系统已经开始打造,芯片工业发展的新未来开始浮出水面。

本文引用地址:http://www.amcfsurvey.com/article/202203/431945.htm因何结盟

UCIe(Universal Chiplet Interconnect Express)联盟包括了英特尔、台积电、三星、AMD、Arm、高通、日月光、Google Cloud、Meta、微软等行业巨头,旨在建立统一的die-to-die(裸片到裸片)互联标准,打造一个开放性的Chiplet生态系统。

Chiplet被看做是延续摩尔定律的重要途径,通过将复杂芯片的不同功能分区制作成单独芯片,再使用先进封装组合在一起,可以突破传统SoC制造面临的诸多挑战(光罩规模极限和功能极限等),大幅降低设计生产成本。

因使用基于异构集成的高级封装技术,Chiplet使得复杂芯片的生产不再受到不同工艺的约束,凭借算力拓展的方式就提升了整体性能,并大幅缩短了生产周期。半导体大厂纷纷开始布局,希望依靠先进封装技术,以差异化的堆叠来整合不同工艺制程,让Chiplet发挥更高效率。

与所有技术一样,Chiplet也面临不少挑战,将不同规格与特性的小芯片封装在一起,散热、应力和信号传输都是重大的考验。最大的问题还是标准不统一,不同厂商开发的Chiplet很难实现匹配和组合,因而限制整个业态的发展。

“UCIe的出现相当于交通规则实现统一,打破了不同工艺和晶圆厂之间的界限。”业界资深人士何凌(化名)告诉爱集微,“之前每个Chiplet组合都需要制定新的传输协议,无论die通过硅桥还是基板连接,供应商都需要进行定制,对设计公司还是供应链来说,复杂度都过高了。”

他进一步解释,“Chiplet都有好几个die,可能来自相同工艺的不同晶圆厂,或是同一晶圆厂的不同工艺,要实现连接就需要特定的die-to-die连接IP,而只有晶圆厂互相同意,才会搭起这个桥。”

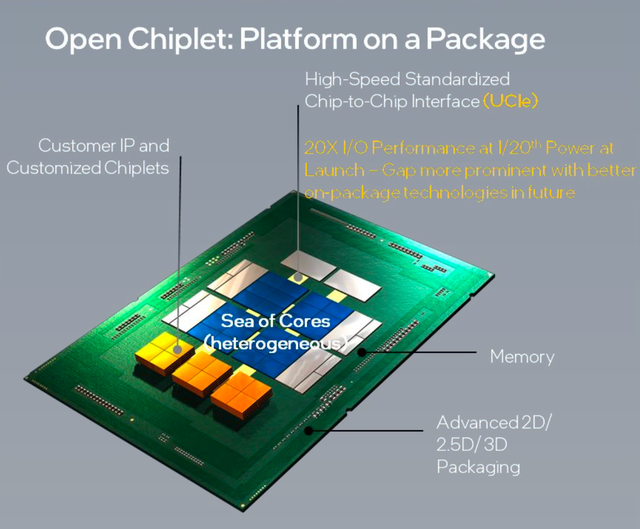

统一的连接标准因此至关重要。英特尔公司IO技术解决方案团队战略分析师Kurt Lender表示:“基于小芯片的SoP架构允许设计人员将来自多个供应商的设计IP和工艺技术整合在一起,但这种模块化和设计自由度只有在设计人员使用标准化、可互操作的硬件时才有效,而跨多个供应商实现标准化硬件的最佳方式就是设置一个每个人都可以使用的单一开放规范。”

UCIe联盟制定的UCIe标准意味着小芯片的接口将标准化,用户可以从多个晶圆厂获得构建Chiplet的小芯片,实现真正的混合配置,“等于打破了各公司之间的壁垒,降低了复杂芯片的开发成本。”爱集微咨询业务部总经理韩晓敏认为这将在提高Chiplet生态系统效率方面发挥关键作用。

英特尔公司表示,UCIe联盟代表一个多样化的市场生态系,将满足客户对于更加客制化的封装层级整合需求,从一个可互通、多厂商的生态系,连结同级最佳芯片到芯片互连和协定。

Arm公司指出,UCIe是一个新的行业联盟,旨在建立一个die-to-die的互连标准,并促进一个开放的Chiplet生态系统,同时满足客户对更多可定制的封装级集成的要求,将一流的die-to-die的互连与协议从一个可互用且多厂商的生态系统连接起来。

联盟使命:突破互联、封装屏障

乐高积木有成千上万种,依靠统一的插口,用户可以实现任何组合。对于Chiplet来说,这种统一的插口就是die-to-die之间的互联接口和协议。

之前的Chiplet设计将die-to-die互连与公司的专有接口结合在一起。要扩大Chiplet的应用范围,需要开放接口进行互连,使不同的小芯片能够相互通信。

互连接口和协议对于Chiplet十分关键,其设计必须考虑与工艺制程及封装技术的适配、系统集成及扩展等要求,还需满足不同类型Chiplet集成对单位面积传输带宽、每比特功耗等性能指标的要求。

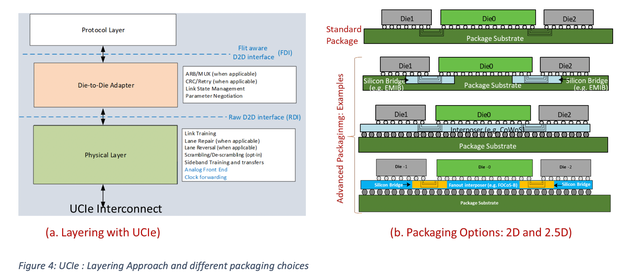

UCIe联盟此次没有采取激进的方法,而是在UCIe 1.0规范中选择了成熟的PCIe(PCI Express)和CXL(Compute Express Link)互联总线标准。

PCIe提供了广泛的互操作性和灵活性,而CXL可用于更先进的低延迟/高吞吐量连接,如内存(CXL.mem)、I/O(CXL.io),以及加速器,如GPU和ASIC(CXL.cache)。

PCIe和CXL已经经过了多重的考验,这意味着UCIe标准正在以一个完整且经过充分验证的协议层开始运行,可以提供可靠的数据传输和链路管理,以及缓存一致性等额外的定制功能。更为重要的是,设计者和芯片制造商都可以利用现有的PCIe/CXL软件,进一步降低了开发功能。

对此,半导体行业人士陈启给出评价:“在UCIe标准落地之后,芯片设计会走向更灵活高效的设计思路,以满足多样化半定制的需求,因此需要不同制程的芯片通过专用总线连接起来,在高效设计和成本方面达到平衡点;UCle标准确定后,未来异构芯片的集成也就铺平了总线标准的道路。”

解决互联只是第一步,要将Chiplet真正结合在一起,最终还要依靠先进封装。这也是Chiplet被划归为先进封装的意义所在。不过,台积电拥有CoWoS/InFO、Intel拥有EMIB、Fovores 3D等,Chiplet使用的先进封装多种多样。为了实现更大的兼容性,UCIe1.0标准没有涵盖用于在小芯片之间提供物理链接的封装/桥接技术。

在UCIe的定义中,Chiplet可以通过扇出封装、硅中介层、EMIB连接,甚至可以通过一个普通的有机基板连接。只要一个UCIe小芯片符合标准(包括凸块间距),它就可以与另一个UCIe小芯片通信。

图UCIe当前所覆盖的封装形式(数据来源:UCIe白皮书)

需要注意的是,Chiplet技术的发展终究会使得小芯片间的互联达到更高的密度,因此需要从传统的凸点焊接转向混合键合(hybrid bonding)。但是,UCIe 1.0标准基本上只对2D和2.5D芯片封装进行了定义,要应对先进封装功能和密度的不断提升,标准本身还需不断升级。

谁人受益

UCIe联盟的发起者中有IDM、晶圆厂、封装厂、IP和系统厂商,谁将是受益者?

作为UCIe联盟的发起人,英特尔认为,将多个小芯片整合至单一封装,在各个市场提供产品创新,是半导体产业的未来,也是英特尔IDM2.0策略的重要支柱。

图英特尔Pat Gelsinger提出IDM 2.0战略

IDM2.0就是把原本只为英特尔内部服务的IDM模式套用到客户上,提供从芯片设计、定制化、晶圆制造到封装测试等传统半导体上下游环节的一条龙服务。

与IDM1.0模式最大的不同就是IDM2.0加入了封装技术。英特尔拥有顶级的3D封装技术,配合Chiplet生态,可有效地缩短纯制程工艺上的差距。

亚马逊、Google、苹果、微软、Meta和特斯拉等科技巨头都曾是英特尔的客户,如今在云端服务和终端产品上,都有计划或已经采用自研芯片,原因之一就是英特尔过去缺乏弹性的定制化服务能力。若英特尔的3D封装技术借Chiplet生态发挥最大功效,有望满足这些客户的高端设计服务需求。

今年2月,英特尔正式宣布一项10亿美元新基金,将优先投资能加速代工客户产品上市时间的技术能力,涵盖IP、软件工具、创新芯片架构和先进封装技术。英特尔还宣布与该基金联盟的多家公司建立合作伙伴关系,打造一个开放的Chiplet平台(Open Chiplet Platform)。此平台将利用英特尔的封装能力和针对英特尔代工服务(IFS)工艺技术的IP优化,并结合包含集成和验证服务,加快客户上市时间。

有资深业内人士指出,“提出IDM2.0,可使英特尔处在可进可退的位置,进一步建立标准语言后,未来有机会去争取更多的客户,退路是如果做得不好,则可以进行外包,也符合2.0计划。”

晶圆厂在当前的Chiplet生态中处于有利位置,加入UCIe联盟将使得优势进一步扩大。晶圆厂积累了大量用于传统芯片的IP核和die,都可以用于开发基于Chiplet的设计。客户选择想要整合的功能,晶圆厂提供解决方案,结合先进工艺和先进封装将不同的Chiplet集成在一起。

台积电早在10年前开始耕耘先进封装,结合自身晶圆代工龙头的实力,快速拉开和对手的差距,同时正大举扩充先进封装产能。台积电先进封装竹南AP6厂去年SoIC部分设备已移入,Info相关部分则目标是今年到位,整体将在今年底量产。

三星先前也已陆续更新异质封装技术,最早在2018年推出首款I-Cube2方案,后续在2020年推出X-Cube方案的3D堆叠设计,去年也已更新I-Cube第四代方案。

何凌认为,晶圆厂如果把先进封装做好,“弯腰”进入更下游的基板领域,将基板的基础打好,有助于实现产业垂直整合的目标。

封装厂也在研究自己的Chiplet策略,但依然采取了类似当前的生产流程。晶圆厂为客户生产芯片,然后将成品芯片送到封装厂,由其负责处理封装集成。“问题是Chiplet更多的是依靠先进封装,属于前道工艺的范畴,所以处在后道工序的封装厂戏份并不多。”一位行业观察者指出。

不过,扇出型板级封装的出现可能改变这种局面。这种封装技术将使得封装厂具备与晶圆厂相抗衡的实力,以日月光为首的封装厂正在积极开发自己的板级封装工艺。

IP公司也将从Chiplet生态中获得更多机会。“即使是大公司也无法承担内部开发所有IP的费用,希望通过第三方IP来节省时间和金钱;同时,UCIe对于IP供应商意味着新的生意,不管是芯片内部传输,还是在机箱中增加UCIe接口,都增加了更多可能性。”何凌说。

不过,最大的机会源自IP的芯片化。“通过标准化协议,IP公司可以把CPU核做成一个芯片,实现实体化,而随着Chiplet方案进一步扩展,Arm A78核可能用台积电的16nm就搞定了,单个小芯片体积变小,整体设计成本就大幅降低了。”何凌认为相当于将Chiplet广义化,若协议推广开来,IP开发难度门槛会降低很多,很多IP公司都愿意加入这个联盟。

Arm公司就表示,可互用性对于解决Arm生态系统、乃至整个行业的碎片化至关重要,“当今,我们看到行业中有很多人正在以独特的方式进行这种的整合;通过UCIe,我们能够推动一个可互用的标准,该标准将同时提供向后兼容的能力。”

最后是微软、Meta、Google一类的系统公司,其已经从自研芯片中得到很多益处。有了成熟的Chiplet生态,他们将会更容易地得到定制化芯片。

UCle联盟的成立只是Chiplet生态建立的头一步,当技术和商业模式逐渐成熟的时候,Chiplet体系中可能还会出现新的商业角色,如供应Chiplet模块芯片的供应商、将Chiplet芯片集成组合形成系统能力的集成商,以及进行工具链和设计自动化支持服务的EDA软件提供商等。所以,UCIe的诞生确实为芯片工业又打开了一扇新的大门。

评论