基于HW2181B的航模无线遥控通信系统设计与实现

(上海东软载波微电子有限公司 200030

本文引用地址:http://www.amcfsurvey.com/article/202011/420279.htm0 引言

HW2181B 是一款高集成度的2.4 GHz ISM频段无线SoC芯片,可应用于无线航模、智能家居、以及其它无线数据传输和远程控制等领域。片上集成高性能、低功耗的RF收发器和32位MCU(单片机)。本设计采用HW2181B SoC单片机作为航模无线遥控通信系统的核心芯片,在单片机的控制下实现航模无线遥控通信系统的遥控器端与接收器端的数据传输及2.4G 通信频道的自动跳频,有效地改善了通信质量和通信距离。

1 HW2181B简介

HW2181B是一款高集成度的2.4 GHz ISM频段无线SoC芯片,片上集成高性能、低功耗的RF收发器和32位MCU。工作电压范围:2.2~3.6V,工作主频最高48 MHz,

片上RF收发器的外围电路简单,只需少数外围被动器件即可构成完整的2.4 GHz无线收发系统。RF 收发器发射功率最大可以到8 dBm ,接收灵敏度可达到-93 dBm@250 kbps、-89 dBm@1Mbps。

片上 MCU内部集成32位ARM Cortex-M0 CPU内核,具备36 kB的Flash程序存储空间。

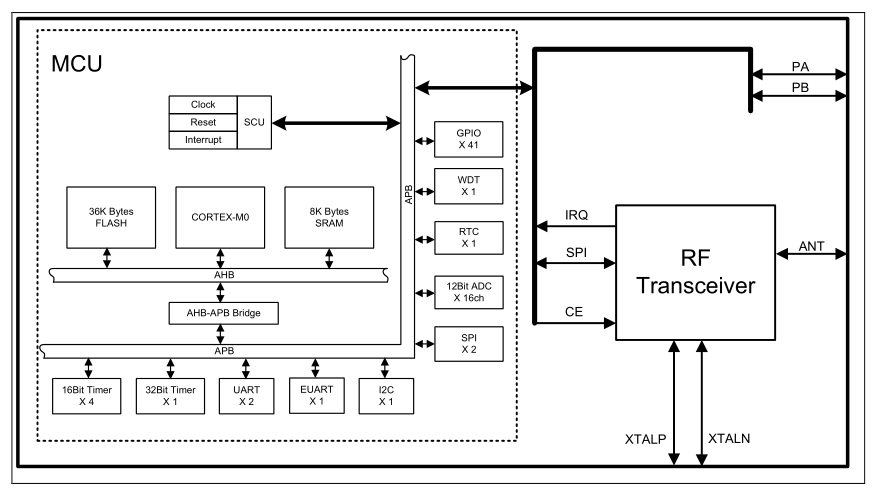

HW2181B单片机系统框图如图1所示。

图1 HW2181B单片机系统框图

2 RF收发器介绍

RF收发器特性:使用国际通用的2.4 GHz ISM工作频段(2 402~2 483) MHz,支持GFSK 调制方式,支持250 kbps / 1 Mbps 两种数据速率,支持数字 RSSI 测量,支持4 PIPE 多逻辑通道传输。

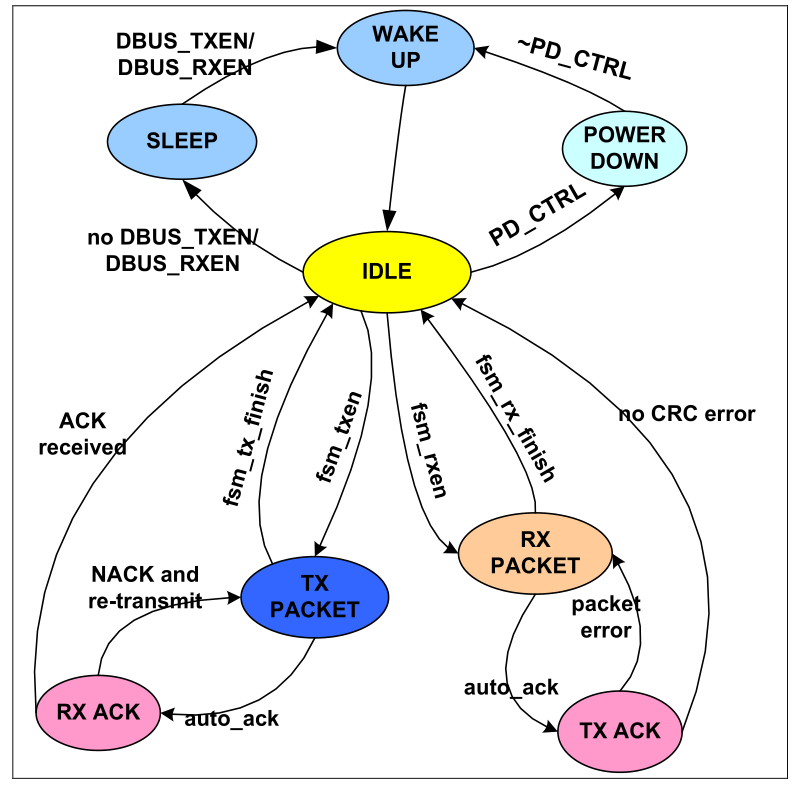

2.1 RF收发器工作模式如图2所示。

图2 RF收发器工作模式

当使能RF收发器DBUS_TXEN并且发送FIFO处于有效状态后,RF收发器进入TX模式。在发送完成之后,RF收发器进入IDLE模式,关闭DBUS_TXEN后,RF收发器进入SLEEP模式。

当使能RF收发器DBUS_RXEN并且接收FIFO处于有效状态后,RF收发器进入RX模式。若FIFO为占用状态不满足接收条件时,RF收发器进入IDLE模式,关闭DBUS_RXEN后,

RF收发器进入SLEEP模式。

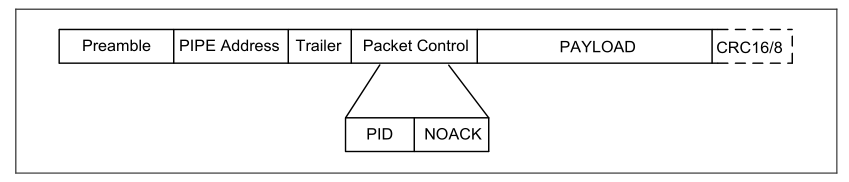

2.2 RF收发器数据包

结构如图3所示。

图3 RF收发器数据包结构

Preamble

支 持 2,4,6…16bytes, 长 度 可 通 过 寄 存 器 PREAMBLE_LEN ( PKTCTRL 寄 存 器 的Bit15-Bit13)配置。

PIPE Address(Syncword)

支持16/32/48 bit, 长度可通过寄存器 SYNCWORD_LEN(PKTCTRL 寄存器的 Bit12-Bit11)

配置。支持4路数据通道,PIPE Address 可通过寄存器0x40~0x47配置。

Trailer

支持 4~18 bit, 长度可通过 TRAILER_LEN(PKTCTRL 寄存器的 Bit10-Bit8)配置。

PID

PID 长度为2 bit,发送时由硬件自动产生。 PTX 每发送1次新的数据包 PID 将自动加‘1’。

PRX 针对当前接收的 PIPE 地址,依据 PID 与 CRC 值确定当前包为新接收包或重传包(重

传包会被丢弃)。PTX 若重发超时,在下一次重新发送时 PID 不累加。

NOACK

此指示位用于当 ACK 功能使能时,PTX 告知 PRX 当前包无需 ACK 的特例情况。可以通过

PTX_FIFOn_NOACK(FIFOnCTRL 寄存器的 Bit4)进行设置。

PAYLOAD

硬件链路控制方式下,每级 FIFO 最大支持 63bytes 的 PAYLOAD,非定长模式 FIFO 的第1个 byte 代表 PAYLOAD 的长度,定长模式 PAYLOAD 长度由寄存器 FIX_PLD_LEN 配置。

软件链路控制方式下,PAYLOAD 的长度由主控 MCU 芯片决定。

CRC

硬件链路控制方式下,支持 CRC16 与 CRC8 两种模式,可通过 CRC_SEL(MISC1 寄存器

的 Bit14)配置。

CRC16 生成多项式为:x 16 +x 12 +x 5 +1

CRC8 生成多项式为 :x 8 +x 2 +x+1

软件链路控制方式下不支持硬件 CRC 功能。

3 系统硬件设计

3.1 原理图设计

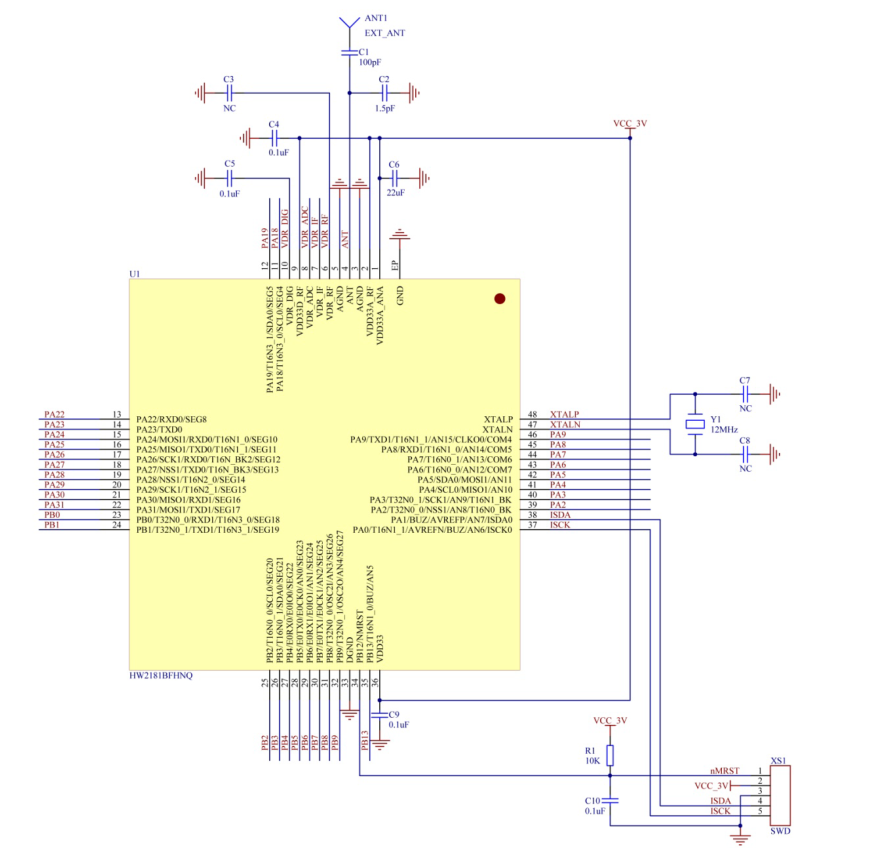

HW2181B 是一款高集成度的 2.4 GHz 无线SoC 芯片,片上集成高性能、低功耗的射频收发器和32位MCU。片上射频收发器的外围电路简单,只需少数外围被动器件即可构成完整的2.4 GHz无线收发系统。HW2181B无线收发系统原理图如图4所示。

图4 HW2181B无线遥控通信系统原理图

HW2181B 应用电路主要由晶体振荡电路、射频匹配网络、电源去耦网络和数字 I/O 四部分构成。

晶体振荡电路支持 12 MHz、16 MHz 无源晶振。根据应用需求的不同,晶振选取原则如下:晶振的频率公差(Frequency Tolerance)越小,收发两端之间的频率差越小,则远距离通信成功率将显著提高。因此远距离应用请尽量选用公差小的无源晶振,推荐使用公差±10 ppm(10-6) 的无源晶振。晶振两边的负载电容 C7 和 C8 一般不需要焊接,只有在一些对频率要求比较苛刻的应用,才需要增加电容进行微调。电容越大则晶振频率越低,但需要注意的是,电容太大会导致晶振不振,由于不同厂家的晶振参数不同,所以具体取值要通过实际调试来确定。

射频前端匹配网络主要完成射频信号谐波抑制、天线端阻抗匹配等功能,该部分元器件选型对通信将产生较大影响。因此,C1、C2请尽量选用高频性能好,精度高、稳定性高的电容,推荐用材质为 NP0(C0G)的电容,至少也要用 X7R 电容。

外围电源去耦电容 C4、C6 和 C9,可以滤除电源上的干扰信号。其中,特别需要注意的是 C6,建议最小取值 10uF,对于一些干扰很大的应用,建议增加到 22 µF 以上。C4和 C9一般取0.1 µF即可。需要注意的是 C5,是芯片内部数字模块的滤波电容,推荐焊接,可以增强数字电路的稳定性。C3 是内部射频模块的滤波电容,一般不用焊接。

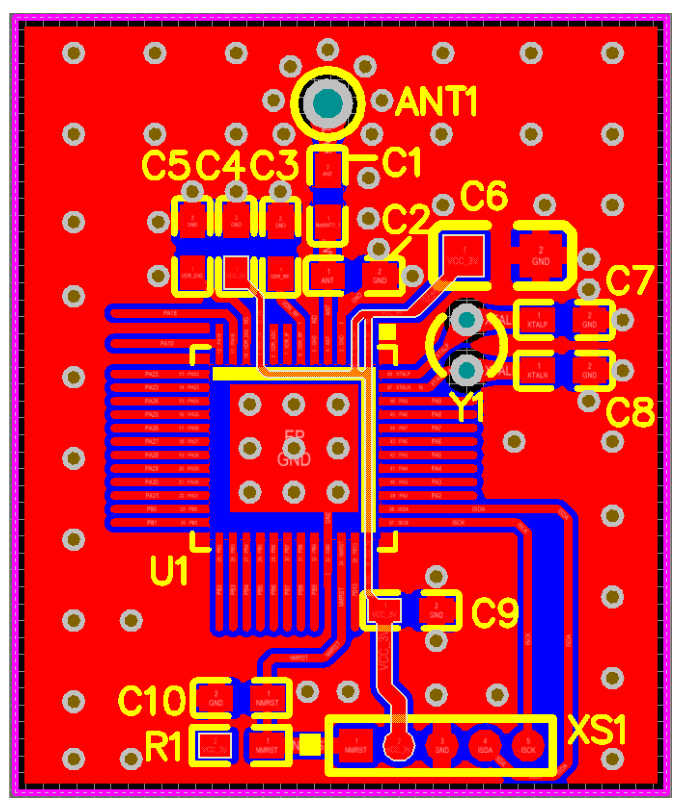

3.2 PCB设计

HW2181B 2.4 GHz无线通信系统对PCB(印制板)设计有比较高的要求,设计不好会影响通信距离。本设计PCB 如图5所示。

图5 HW2181B无线遥控通信系统PCB

射频 PCB 对于布局和布线都有一定的要求,注意事项如下。

1) 需要特别注意的是ANT 脚有直流电压输出,所以推荐使用电容方案,此方案可以外接 PCB天线和导线天线。

2) 芯片底部中间的大焊盘(EP)脚必须接地,建议在此焊盘上添加 9 个均匀排列的接地过孔。推荐过孔尺寸为 0.3 mm,减小漏锡的风险。3 脚和 5 脚不需要和底部大焊盘连接,主要用于射频信号隔离。

3) 射频器件必须优先布局布线。C1 和 C2 是射频匹配元件,必须尽可能靠近芯片的 ANT脚(PIN4),推荐的布局方式是 C1 垂直放置,C2 水平放置。射频电路(包括射频走线、器件和天线接口)周围都要包地,并均匀放置一些接地过孔。

4) C4 和 C6 是芯片电源的滤波电容,是系统稳定工作的保证,不能省略。

特别是和芯片 PIN1和 PIN2 连接的 C6,应该选取大容量电容,建议最小取值为 10 µF,推荐 22 µF 以上。C5 推荐焊接,可以增强芯片的可靠性。C3 电容一般不需要焊接,可以在PCB板上预留位置。

5) 芯片内部RF收发器的电源管脚是PIN1、PIN2、PIN9,MCU的电源管脚是PIN36,它们在内部无连接,所以需要在外部连接到电源上。RF 收发器的电源线可以在芯片管脚和中间大焊盘(EP)之间的区域之间走线(见图中的高亮线),由于是在芯片底部,为了避免短路,需要在电源走线上增加一层丝印保护。电源线尽量不要在底层走线,以免破坏底层地平面的完整性。

6) 晶振两边的C7和C8电容一般不需要焊接,只有在需要调整晶振频率时才使用,可以在PCB板上预留位置。

4 遥控器和接收器通信算法概述

1) 系统根据遥控器端产生的5个随机地址码及1-16组成的数进行哈希运算,在80个频点中生成1个含16个频点的跳频表,跳动时间间隔为15 ms,精度为±500 µs,采用hash 算法算出此跳频表,预先存储1个16个频点的hash table在遥控器端,对码时传给接收器端,接收器端进行表的存储。

2) 遥控器端和接收器端对码时均使用同一个16个频点的table,同时存储在遥控器端和接收器端。

3) 接收器端通过依次停留在跳频表的每个频点搜索遥控器端数据,每频点最多停16×15 ms+2 ms=242 ms,收不到再依次切换到下一个频点,收到后即按跳频表跳动,同时进行时间同步清零操作。接收器端在计算出的监听点+2 ms区间内监听,收到后即进行同步清零,没收到计算下一频点时间并等候。

5 结语

本文介绍的基于HW2181B SOC MCU航模无线遥控通信系统的设计与实现具有很好的实用价值和成本优势。特别是本设计采用的通信跳频算法,提高了系统的抗干扰能力,有效地改善了通信质量。基于HW2181B方案的航模无线遥控通信系统在众多航模产品研发企业中得到广泛的应用,获得开发工程师的一致好评。

参考文献:

[1] 上海东软载波微电子有限公司.HW2181B数据手册[Z].

[2] 上海东软载波微电子有限公司.东软载波单片机应用系统[M].北京:北京航空航天大学出版社,2017.

(注:本文刊登于《电子产品世界》杂志2020年11期)

评论