后CMOS制程时代 摩尔定律如何再延续30年

摩尔定律(Moore’s Law)虽然是英特尔(Intel)共同创办人Gordon Earle Moore所创,至今超过50年历史,但在贡献让摩尔定律继续推进的角色上,英特尔绝非最大且唯一的贡献者,如今在半导体晶圆制造业界努力下,摩尔定律正在经历再次演进期。

本文引用地址:http://www.amcfsurvey.com/article/201910/405961.htm

日前在美国加州史丹佛大学(Stanford University)举办的2019年Hot Chips大会上,现任台积电副总经理黄汉森(Philip Wong)进行的一场演说,便就既有半导体平面(Planar)制程技术以及采用其它更先进技术,如何持续维持摩尔定律不死进行说明。他认为,摩尔定律不仅没有消亡,也没有减速,甚至没有生病!

从英特尔角度看,也认为摩尔定律还在持续演化。如英特尔(Intel)技术开发部门制程与产品集成主任Ramune Nagisetty认为,摩尔定律原先是关于每晶体管成本和多少晶体管可搭载于单一芯片的律则,如今更新的运算系统架构方式透过排除传统阻碍,以及提升效能、功耗与成本,正在驱动摩尔定律持续演化。

CMOS制程仍是短期推进微缩最佳途径

黄汉森甚至认为,在有合适的技术下,摩尔定律仍可存续30年。至于要如何维持摩尔定律存续,唯一的重点在不断提升晶体管密度,进而可持续提供更佳的效能以及能源效率表现。The Next Platform报导,黄汉森指出,只要业者能够持续在更小芯片空间内放入更多具更佳能源效率的晶体管,就能持续让摩尔定律存续,不论所采用实现这个晶体管密度持续提高的方式为何。

在此情况下,短期内要能持续推动摩尔定律前进,仍必须仰赖既有持续推出更先进CMOS制程的技术,让晶圆制造端能够量产闸极长度(Gate Length)更小的晶体管。以台积电为例,目前的进展是在蚀刻7纳米晶体管,并朝5纳米制程推进。

黄汉森指出,5纳米节点的设计生态系统已准备就绪,台积电已开始进行风险试产。由此显示,台积电制程节点以及设计工具已经完成开发,并正进行可投入量产的晶圆生产阶段。台积电方面日前表示,该公司计划2020年上半开始量产5纳米芯片。在此情况下外界分析,台积电甚至可能正在发展3纳米制程节点技术。

即使如此,上述都仍停留在既有的传统平面制程,黄汉森认为,最终传统平面制程终有一天将不再能进行微缩。但这不代表晶体管密度持续微缩的进行就会终结。有业界人士指出,摩尔定律在台积电、三星电子(Samsung Electronics)以及GlobalFoundries等全球主要晶圆制造厂商中,依然很好的扮演著角色。

AI、5G驱动下阶段半导体制程演进

如黄汉森所言,在半导体晶圆制造产业仍在进行许多技术创新,以能在Dennard微缩定律(Dennard Scaling)终结后,持续推进晶体管密度微缩保持在上升曲线,特别是如采用应变矽晶(Strained Silicon)、高介电常数金属闸极(High-K/Metal Gate;HKMG)技术,再者是引入3D结构的鳍式场效晶体管(FinFET)制程技术。如今业界也在探索名为「设计技术协同最佳化」(Design Technology Co-Optimization;DCTO)的技术,以推进朝7纳米制程以下迈进。

这些新制程技术的创新,都是为了让半导体晶圆制造端,能够跟上科技产业终端应用,对具备更快运算速度及更佳硬件能源效率的更新式运算平台推出的需求所生,这样的演进过程至今已有40年左右。

从1970年代迷你计算机(minicomputer)作为开端,到1980年代的PC崛起时代,再到1990年代的互联网兴起,再到2000年代至今的行动运算浪潮,每一代都有赖全球半导体制程的不断微缩演进,带动晶体管密度不断微缩,以能推出效能及功耗更佳、符合新科技浪潮的更高运算需求,进而形成当前全球科技产业供应链现况,并创造一个愈来愈科技渗透的社会环境。

随著行动时代发展至今逐渐趋于成熟、成长性逐渐趋缓,黄汉森认为,人工智能(AI)以及5G将会是下一阶段推动半导体制程微缩前进的主要推动力。

2.5D、3D结构接棒 解决长期微缩困境

未来能让摩尔定律持续推进的创新技术方面,从短期来看,目前小芯片(Chiplet)技术在2.5D结构中建立的多芯片封装技术,将有助增加整体运算以及存储器密度,即使小芯片技术途径没有创造任何晶体管微缩的效果。因此在小芯片技术途径发展上,黄汉森指出,让个别小芯片制程节点的重要性,不如如何将这些元件集成在同一个封装中来得重要。

在这部分,台积电藉由自有CoWoS(Chip-on-Wafer-on-Substrate)技术,掌握了自有2.5D封装制程版本,与此相较,英特尔「崁入式多芯片互连桥接」(Embedded Multi-Die Interconnect Bridge;EMIB)封装技术则是相应的竞争技术。

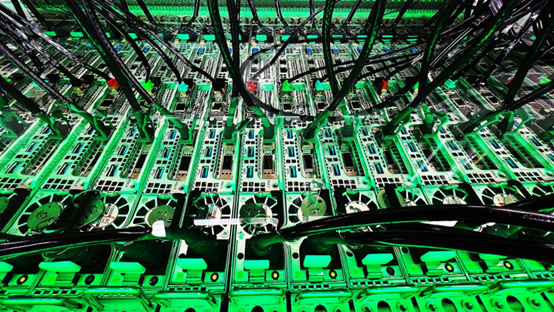

CoWoS透过在矽载板(silicon interposer)上方安装小芯片以及合适的存储器装置,并以矽导通孔(Through Silicon Via;TSV)进行连结的方式,进行多芯片封装作业。NVIDIA的Tesla V100 GPU加速器即最典型的CoWoS技术产物,其将1个GV100 GPU和高带宽存储器(HBM)模块进行封装。

其它如超微(AMD)、英特尔以及赛灵思(Xilinx),也都各自在发展自有小芯片技术途径。如英特尔Nagisetty指出,藉由先进封装技术,能以更具创新的方式将各个更小的小芯片接合在一起,Stratix 10现场可程序化逻辑闸阵列(FPGA)即英特尔首款采用小芯片以及先进封装技术途经开发的芯片产品,下一代Agilex FPGA英特尔也将持续突破既有小芯片与先进封装技术的极限。能够快速推出客制化芯片产品,具备很高的价值。

Nagisetty也称小芯片技术途径一大优势,在于为芯片创新创建一个平台,因小芯片技术可让小型、无晶圆厂芯片业者投入设计,让业者无需设计整个CPU或产品,根据自身特定专业进行创新设计。例如美国国防高等研究计划署(DARPA)的「DARPA CHIPS」计画中,就有几款小芯片设计成为英特尔FPGA平台。

但2.5D结构仍有限,3D封装技术才是推进微缩的长远解决途径,例如台积电的N3XT(Nano-Engineered Computing Systems Technology)架构。N3XT为基于全新纳米材料以及存储器与逻辑良好集成的3D单片(monolithic)设计。

虽然自2015年在学术圈就可见N3XT技术,如今才有台积电认真看待这项技术,有助在台积电推动下未来导入商用化。有研究显示,以各式机器学习(ML)推论为评测基准,采N3XT生产的半导体装置比采2D制程的装置,效率提升介于63~1,971倍之间。

黄汉森指出,N3XT系统包含多层的能源效率逻辑层、高速存储器,以及高容量非挥发性存储器,以交错方式堆叠在一起,并全都位在传统的矽逻辑晶粒之上,并由金属层间通孔(Inter-Layer Via;ILV)来连结这些不同的元件,这也是一大技术关键。与微米尺寸的矽导通孔(TSV)不同的是,ILV能达到更小的纳米尺寸。

对3D封装技术而言,存储器和逻辑的交错堆叠更具重要性,因为这可缩短元件彼此之间的距离,进而有助实现5G以及AI等应用对高带宽、低延迟通讯的需求,这是传统CMOS无法做到的。因为逻辑晶体管需要约摄氏1,000度才能进行适当的蚀刻,这样的高温可能会在制造过程中导致邻接的其它元件毁坏。

低温材料、新式存储器扮演助攻角色

制程技术之外,过去几年也可见在开发在相对低温情况下,适合于制造高效能晶体管的新材料,此即过渡金属二硫属化物(Transition Metal Dichalcogenides;TMD)。TMD材料的优势在具备更高的电子移动率,让电荷在更薄的通道中能够更轻易移动,有助于小于2~3纳米晶体管的开发。对此黄汉森指出,台积电目前在研发阶段已开发出采二硫化钨(tungsten disulfide)打造的实验性质TMD晶圆。

纳米碳管(Carbon Nanotube)则是另一可行的纳米材料。黄汉森指出,已可制造出采纳米碳管材料的实验性质晶圆,并展现出不错的半导体行为。实际上目前在业界已可见以纳米碳管为基础开发的逻辑和SRAM装置的原型设计问世,包含近期麻省理工学院(MIT)研究人员开发的RISC-V实作产品。

3D集成最适合采用的存储器方面,黄汉森认为包含SST-MRAM、PCM、ReRAM、CBRAM以及FERAM,这些存储器都具备可随机存取、非挥发性等特性。目前已有部分投入商用化阶段,诸如三星电子(Samsung Electronics)的嵌入式MRAM、英特尔3D XPoint以及Everspin的MRAM。

整体而言,虽然黄汉森未明确揭露上述新技术将如何延续摩尔定律达他所称的30年之久,但也算是为晶圆制造如何从平面制程,演进至2.5D、3D结构制程,以及所能采用的其它潜在技术及材料,勾勒一个可持续带动微缩及晶体管密度提升的技术途径,静待全球半导体晶圆制造端提出可商用化解决方案,实现摩尔定律的延续。

评论