基于CPRI协议的5G高速光纤接口研究

李奥,徐兰天

本文引用地址:http://www.amcfsurvey.com/article/201907/402133.htm(中国电子科技集团公司第四十一研究所,安徽 蚌埠 233010)

摘要:“高速率”是5G通信的主要特性之一,为满足即将到来的5G高速数据传输需求,需要提供一种高速稳定的数据传输接口。本文就光纤传输结合支持多级传输速率的CPRI协议,设计出一种高速光纤接口控制板,控制板采用高性能的Virtex-6系列FPGA作为主要控制芯片,经过仿真验证,该控制板支持近10Gbit/s速率数据的稳定传输,具备高速的通信传输能力,完全支持5G通信的高速率传输。高速光纤接口控制板可用于多种5G设备的研究与开发,在5G开发行业与其它高速率数据传输场景具有很好的应用价值。

*项目基金:中国电科技术创新基金项目《微波毫米波大带宽大规模MIMO测试技术研究》

0 引言

新一代移动通信技术5G通信正在如火如荼的推进当中,5G相比4G带来了数据流量和传输速率的大幅度提升,其典型用户数据速率将提升10~100倍,峰值速率可达10 Gbit/s [1] 。高速的数据传输速率给传统的双绞线传输介质带来了巨大压力,而光纤通信具有传输速度快、损耗低、容量大等特点, 非常适用于高速数据传输,不过光纤接口相比于传统网络传输介质的接口也更为复杂。由爱立信,华为,NEC,西门子和北电组成的通用无线接口联盟规定了CPRI协议标准,CPRI作为通用公共无线接口提供了无线控制设备(REC)与无线设备(RE)之间的通信标准,通用的开放标准极大节约了产品成本,提高了其通用性和灵活性,有效地解决了5G通信下数据的高速传输需求。因此,基于CPRI协议的高速光纤接口研究具有重要的价值与意义。

本文采用Xilinx公司的Virtex6系列芯片与高性能DSP处理器相结合,设计出可控制4个光口收发的控制板。可采用回环测试方法对光口收发状态进行测试,构成一套可实现多级速率、数据收发状态实时分析的高速光纤接口板卡。

2 CPRI协议概述

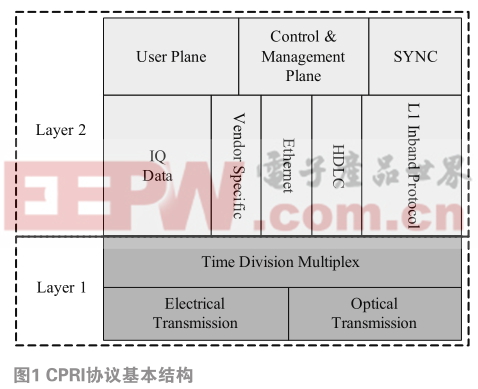

CPRI协议定义了物理层(Layer 1)和数据链路层(Layer 2),其中物理层包括电学传输接口和光学传输接口,数据链路层支持同向和正交数据、厂商特定信息、以太网、高级数据链路控制以及L1带内协议 [2] ,其基本结构如图1所示。

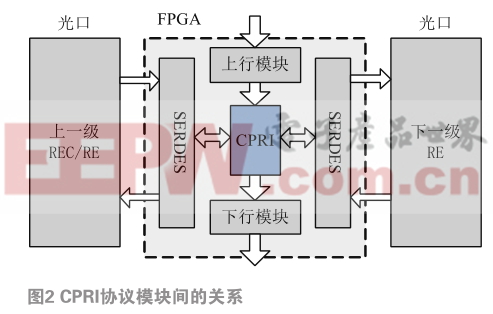

CPRI协议支持从614 Mbps到9830 Mbps的多级速率等级,目前市场上的专用高速接口芯片很少能够支持CPRI的9830 Mbps速率等级,而支持该速率等级的FPGA型号较多,故本文选用性价比较高的Virtex6系列FPGA芯片。CPRI协议能够有效处理REC与RE或RE与RE之间的光纤连接,其可将数条并行CPRI数据链路进行串行化处理,从而实现光纤的超高速传输,CPRI协议模块间的关系如图2所示。

3 高速光口控制板设计

3.1 硬件架构设计

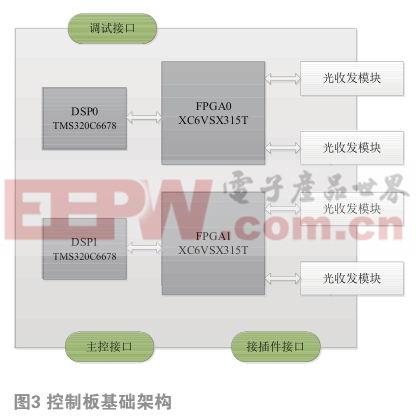

本文所要研究的高速光纤接口基于Virtex6系列FPGA芯片与高性能DSP处理器所设计的控制板,光口传输速率高达10Gb/s。控制板能通过预留的主控接口与上位机之间通信,并通过DSP来控制数据的收发, FPGA来控制光口的通信以及数据的整理功能,整个控制板的基本架构如图3所示。

控制板包含四个光收发模块,分别由一个DSP和一个FPGA控制两个光收发模块,DSP具有较高的工作频率,其内部集成了网络MAC接口,外接一个物理层芯片就可以实现高达千兆的网络通信。本文介绍的控制板基于多核数字信号处理器TMS320C6678,可实现单个芯片连接两个千兆网口,这两个网口可以各自独立传输数据,也可以联合传输数据,提高了实际的数据传输速率。FPGA与DSP之间可通过FIFO进行速率匹配,本文中控制板选用Xilinx公司型号为XC6VSX315T的FPGA作为主控芯片用来控制光纤接口的主要功能,主要功能是完成光收发模块的使能控制、光传输的链路管理以及数据传输的控制,同时XC6VSX315T包含丰富的Slices及多个用户I/O,可以满足控制板的电路设计要求和后期扩展与增强功能的设计,XC6VSX315T还包含5组GTX数据收发接口,每组GTX通道的传输速率最快可达6.6 Gb/s,可以满足光纤接口的高速率要求 [3] 。此外,控制板还设计了主控接口,用于实现与上位机之间的通信,设计调试接口用于控制与调试,设计接插件接口用于外接其它接插件,很好的提高了其灵活性与可扩展性。

整个控制板基于VPX架构,主体芯片除两片DSP及两片Virtex-6 FPGA外,还包括1个RapidIO Switch。每片FPGA通过EMIF总线连接一片DSP,预留的调试接口可插接FMC子卡,FPGA可连接FMC子卡进行调试。FPGA芯片外挂接2簇32 bit DDRIII SDRAM,最大容量支持2 GB。FPGA与DSP进行的所有信号处理均通过SRIO连接板上一片8端口SRIO交换芯片。DSP芯片外挂最大容量支持2 GB的DDRIII SDRAM。两片DSP之间通过HyperLink进行高速直接互联。两片FPGA之间通过GTX以及若干LVDS信号互联。控制板设计符合工业级要求,其主体芯片架构如下图所示。

3.2 软件架构设计

高速光纤接口控制板由FPGA作为主控芯片来控制光纤接口的主要功能,本次设计采用FPGA与CPRI的结合来实现光口的多级速率,控制工程采用Verilog硬件描述语言来作为设计语言,Verilog语言因其简单易读,稳定可靠等优越性逐渐发展成为目前使用最为广泛的硬件描述语言。使用Verilog描述硬件的基本设计单元是模块,通过模块的相互连接调用来实现复杂的电子电路,模块中可以包括组合逻辑部分的逻辑电路图、逻辑表达式、逻辑系统所完成的逻辑功能以及过程时序部分 [4] 。本文使用Xilinx Vivado 2017.2集成开发环境来实现高速光纤接口控制板的功能设计。

本文采用标准的FPGA的逻辑设计的基本方式,模块化相应的功能,根据功能进行模块划分可分为时钟管理模块、数据控制与监测模块和CPRI IP核的调用模块三个模块,另外还有顶层模块负责调用各子模块以及数据接口。

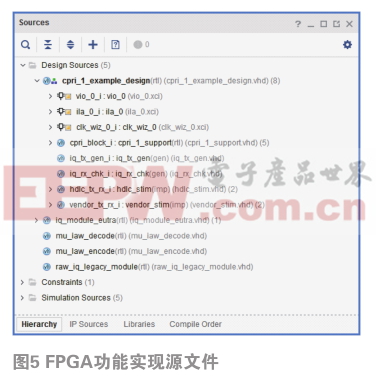

控制板的主控芯片主要实现部分有:顶层模块(cpri_1_example_design),全局时钟管理模块(clk_wiz_0_i: clk_wiz_0),数据监测模块(ila_0_i: ila_0),光口数据控制与产生模块(iq_tx_gen_i: iq_tx_gen),光口数据接收模块(iq_rx_clk_i: iq_rx_chk),以及工程约束文件(cpri_1_example_design.xdc)等。

FPGA内部CPRI在发送端完成8 B/10 B编码和并串转换,在接收端完成8 B/10 B解码和串并转换。通过调用监测模块设置的监测脚可以观测时钟状态及光口数据的收发状态。发送模块中,CPRI的标准16位数据拆分为高8位和低8位,使用FPGA的DDR模块将两部分数据拼接成DDR数据发送出去;接收模块将收到的DDR数据并行传输给FPGA,经过同步与拼接后得到16位的CPRI数据,最后数据传给CPRI模块来进行解帧处理。

本次的光口数据传输过程中使用的CPRI协议已经验证是稳定可靠的传输协议,并封装成可直接调用的IP核,该协议核内部封装了高速串行数据接口硬核,可编程逻辑器件通过绑定GTX通道进行数据的收发交互。单个GTX通道的数据传输速率可实现多个速率级别,最高可达将近10 Gbit/s,根据不同的需求可以多个通道的组合使用,从而可实现几十Gbit速率甚至上百Gbit速率的数据传输,在实验测试中,所调用的CPRI核可以方便的设置多个等级的CPRI线性速率,从而可以很好的研究光口在不同速率下的收发状态 [5] ,下图所示为可调用的CPRI协议的IP核界面。

4 高速光纤接口测试

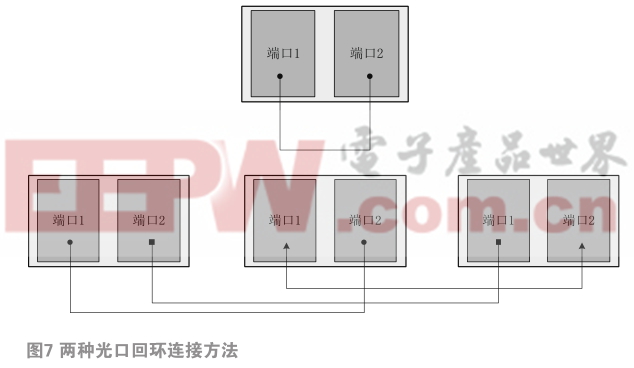

本文采用光口回环测试方法对高速光纤通信系统进行测试,使用光模块和光纤线缆将一个或多个光收发模块构成回环,通过数据监测模块设置的监测脚观测光口的收发状态进行分析。SFP+光收发一体模块包含两个光纤接入端口,分别可用作发射端口与接收端口,并且体积小、易插拔,能够很好的满足本文的测试要求。为提高测试精度及测试效率,本文分别采用单光口自回环连接方式及三个光口构成回环连接方式进行测试,连接方法如下图所示。

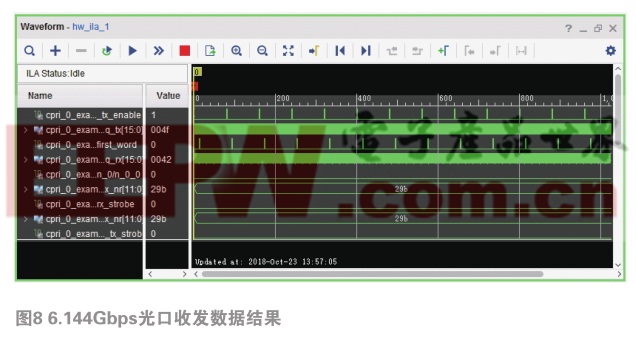

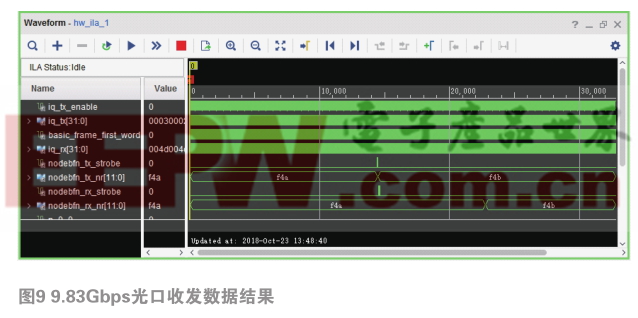

为了验证光纤通信系统能否满足5G通信的高速率传输要求以及数据传输的可靠性,本文分别就6.144 Gbps和9.83 Gbps两个CPRI速率等级进行了测试。首先在测试文件中定义了一个数据产生模块,发送端产生的测试数据通过光模块端口输出,经过光纤回环到另一个光模块端口。数据监测模块定义了发射端监测脚和接收端监测脚分别用来监测发射端口与接收端口的数据状态。在6.144 Gbit/s速率下,定义16位数据监测脚,在9.83Gbps速率下定义32位数据监测脚。

采用Vivado 2017.2软件中的BehavioralSimulation进行仿真验证,经验证,两种速率等级下光纤通信系统均能正常收发数据,并且满足5G通信的基本指标。

5 结论

本文为满足5G高速通信需求,设计了一种基于CPRI协议的高速光纤接口控制板,该控制板具有高性能的数据处理能力和高速的传输通信能力。通过在6.144 Gbps和9.83 Gbps两个速率等级下的测试验证,高速光纤接口控制板具有较好的稳定性与可靠性,并且满足5G通信的基本指标。该高速光纤接口控制板可用于5G信号发生器与5G信号测试装置等设备的研究和开发,对5G通信技术的发展与普及具有重大意义。

参考文献:

[1]屠方泽.5G面临的测试挑战及解决方案[J].电子产品世界,2017(5): 18-19.

[2]马志刚.CPRI原理及测试解决方案 [J].电信网技术,2010(5): 68-70.

[3]Xilinx.Virtex-6 Family Overview [Z].America: Xilinx Inc,2015.

[4]胡泽文.基于CPRI协议的光纤通讯设计与实现 [J].电子元器件应用,2011(2): 27-30.

[5]章洁.基于FPGA的高速光纤通信IP核研究设计[J].数字技术与应用,2015(5): 29-30.

作者简介:

李奥(1993-),男,助理工程师,主要研究方向:信号与信息处理

本文来源于科技期刊《电子产品世界》2019年第7期第36页,欢迎您写论文时引用,并注明出处

评论