采样点测试的原理和设计

采样点是接收节点判断信号逻辑的位置,采样点对CAN总线来说极其重要,尤其是在组网的时候,多个节点尽量保持同一个采样点,若网络中节点采样点不一致会导致同样的采样频率出现采样错误,进而会使整个网络出现故障。

本文引用地址:http://www.amcfsurvey.com/article/201903/398465.htm01 采样点的规则及原理

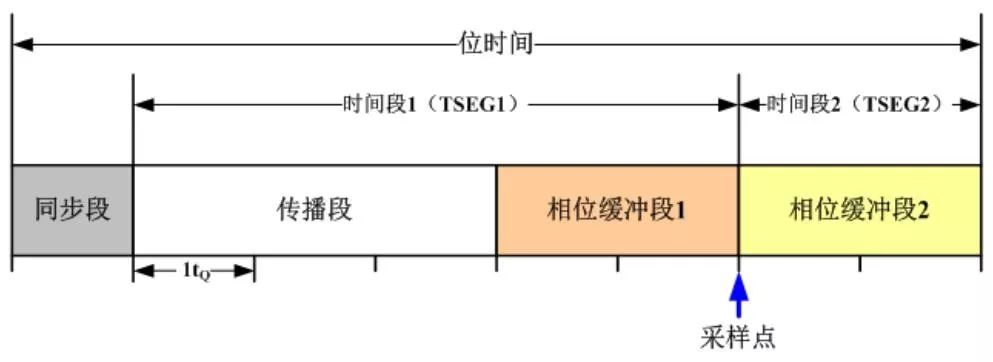

CAN 协议里将一个位时间分为同步段、传播段、相位缓冲段 1 和相位缓冲段 2。这些段又由称之为Time Quantum(以下称为Tq)的最小时间单位构成。1位由多少个Tq构成、每个段由多少个Tq构成等是可以设定的。通过设置bit时序,使得可以设定一个采样点以使总线上多个单元可同时采样,所谓采样点就是在这一时刻总线上的电平被锁存,这个锁存的电平作为位的值。采样点的位置在相位缓冲段1(PBS1)的结束处。

图1 CAN 位时间结构图

同步段(SS):多个连接在总线上的单元通过此段实现时序调整,同步进行接收和发送工作,边沿包含在此段中;

传播时间段(PTS):用于补偿网络上所有的物理延迟;

相位缓冲段1(PBS1)和相位缓冲段2(PBS2):当信号边沿不能被包含于(SS)段中时,可在此段进行补偿;

采样点:读取并解释总线上各位值的一个时间点。

采样点位置如图1所示,它是读取总线电平,并将读到的电平作为位值的点,所以从一个位的开始到采样点的时间占一个完整位的总时间的百分比就是所求的采样点的值:sample =(1+TSEG1)/(1+TSEG1+TSEG2)。

02 采样点测试原理

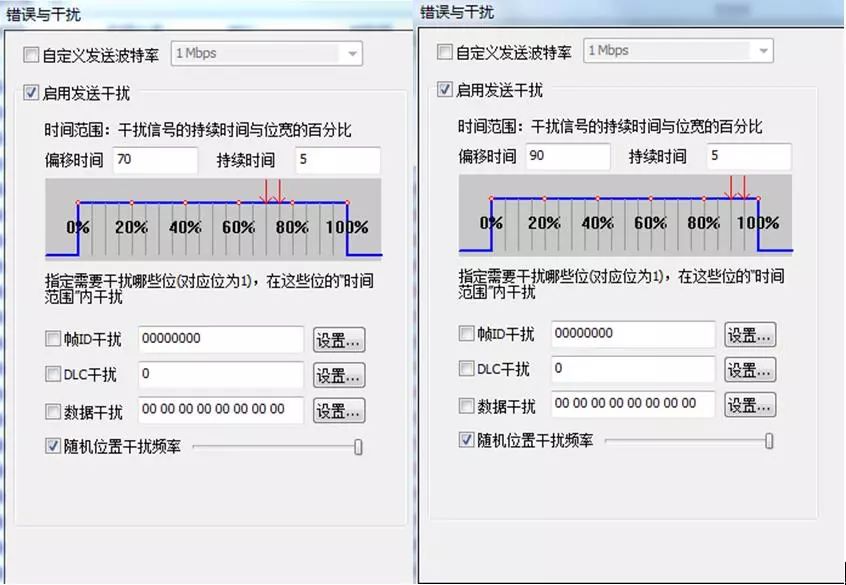

测试原理:波特率采样点是CAN节点判断位逻辑值的判断点。采用干扰的手段,将采样点位置的逻辑电平破坏,则这个CAN报文将出现错误。以此就可以确定干扰的位置为采样点位置。如图2所示,使用我们的CANScope-Pro的错误与干扰功能,可以调整需要翻转的位偏移时间与持续时间,发送此错误的报文给DUT。通过递进式移动干扰位置,查看总线出现错误帧的情况,则出现错误帧的偏移时间(图中红色箭头)为采样点位置。

图2 采样点测试原理

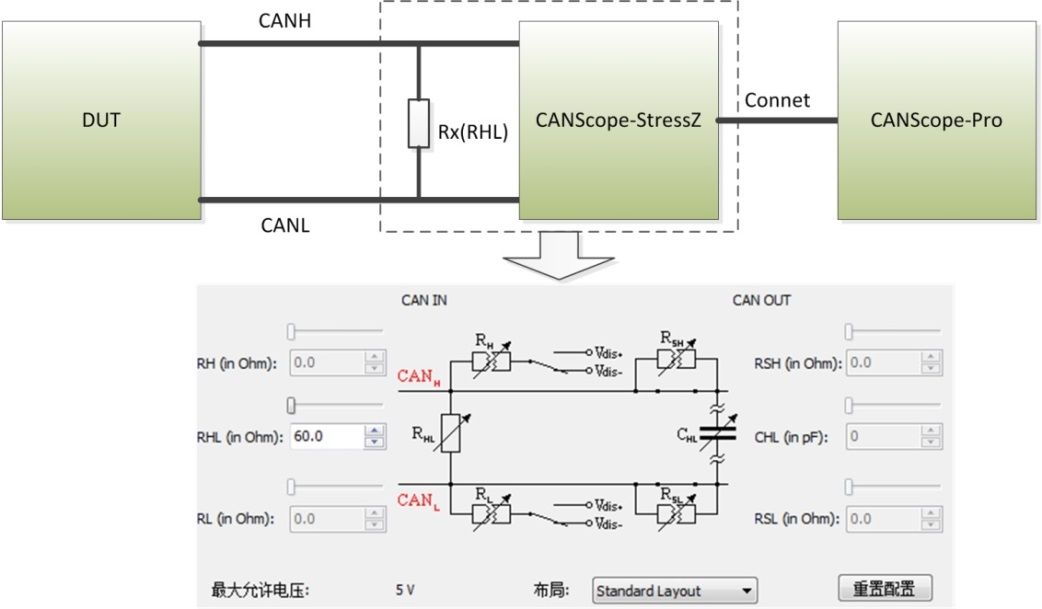

本测试使用CANScope-Pro和CANScope-StressZ。需要DUT上电后,初始化控制器后,不发送CAN报文,方便进行测试。CANScope可以勾选总线应答。如图所示,进行测试连接。使能CANScope-StressZ的RHL为60欧。

图3 采样点测试连接

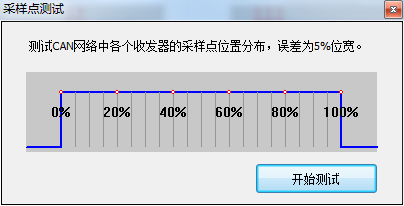

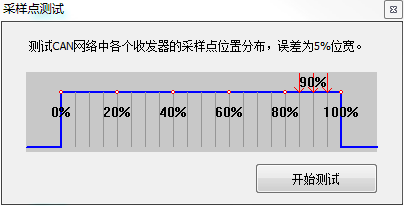

执行CANScope-Pro的“采样点测试”功能,如图4所示。点击开始测试后。

图4 采样点测试

稍等片刻,即可出现测试结果,如图5所示,测试出来的采样点结果为85%~95%。

图5 采样点测试结果

03 常规采样点的设计

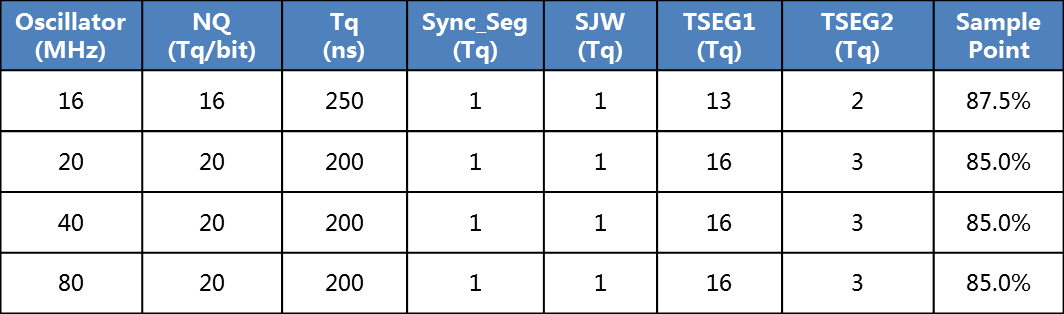

采样点对CAN总线来说非常重要,在组网的时候,多个节点应尽量保持同一个采样点,且最好在但不超过7/8位时间点上,标准中也给了如下几个例子。

关于采样点的计算:

sample =(1+TSEG1)/(1+TSEG1+TSEG2)。

例如上面的计算举例:晶振时钟频率16M, SJW为1个Tq, TSEG1 为13, TSEG2为2,则采样点计算带入上面的公式,sample =(1+13)/(1+13+2)=87.5%。

最后建议大家尽可能的把采样点设置为 CiA 推荐的值:

当波特率 > 800K采样点75%;

当波特率 > 500K采样点80%;

当波特率 <= 500K采样点87.5% 。

如有任何疑问,可以:1、添加小Z微信号、拨打ZLG立功科技·致远电子官方技术热线.

评论