基于Nios软CPU内核的FPGA非线性校正方案

1. 引言

本文引用地址:http://www.amcfsurvey.com/article/201809/389163.htmOFDM能有效抑制多径信道引起的深度衰落、抵抗脉冲噪声和具有较高的频谱效率的特点。但是OFDM的传输符号是多载波的QAM信号经过IFFT处理后得到的结果,由于这种处理是线性相加的关系,当IFFT的输入中存在相位一致的某些点时必然有较高的峰平比,对发射机线性度提出了非常高的要求[1]。射频功率放大器是发射机系统中非线性最强的器件,特别是为了提高功率效率,射频功放基本工作在非线性状态,因此线性功率放大器设计技术己成为线性化发射机系统的关键技术。为了既保证整个系统的效率,又避免信号由非线性造成的失真[2],非线性校正技术随着通信行业的发展变得日益重要。

2. 非线性校正方法介绍

OFDM信号高的PAPR值引起系统非线性失真,主要体现在功率放大的过程中,这本身就是由大功率放大器(HPA)的非线性特性所决定的。

为了获得高效率和线性的HPA,必须消除其非线性失真,采用适当的外围电路对HPA的非线性特性进行线性化纠正,使HPA和线性化电路在整体上呈现对输入信号的线性放大效果[11]。目前,常用到的HPA线性化方法有功率回退法、负反馈法、前馈法和预失真法[7]。无论何种方法,其目的都是为了在保持较高发射效率的同时,获得较好的线性输入输出特性。

2.1 传统非线性校正技术

在线性化技术出现以前,为了避免由于功率放大器非线性引起的信号失真,系统设计者通常选用功率回退法,即把功率放大器的信号输入功率降低,使功率放大器工作在线性工作区内,远离非线性饱和区,从而改善功率放大器的互调失真[12]。功率回退法原理简单且易实现,不需要任何附加设备,但这样做的同时会使功率放大器的效率大为降低,从而影响整个系统的效率。

为了既保证整个系统的效率,又避免信号由非线性造成的失真,线性化技术成为通信领域的一种重要技术。一般而言,传统的线性化技术分为开环和闭环两类,闭环(例如笛卡尔环和极性环)实际上是一种反馈技术,可以获得较高的线性度,但稳定性差,且只能处理窄带数据,不适合多载波系统。而开环的校准精度不如闭环,但处理带宽大,稳定性高。前馈技术作为另一类线性化技术,具有闭环的精度和开环的稳定性和处理带宽,但实现复杂,成本很高,而且调试困难。

2.2 数字基带预失真技术

线性化技术发展中非常重要的一步是预失真技术的出现,预失真技术最初应用于模拟通信系统中的射频部分,后来随着数字信号处理(DSP)技术的发展,预失真线性化技术也可以在数字域内实现,形成数字预失真技术。数字预失真技术主要应用于基带或中频,极少应用处理速率要求极高的射频。

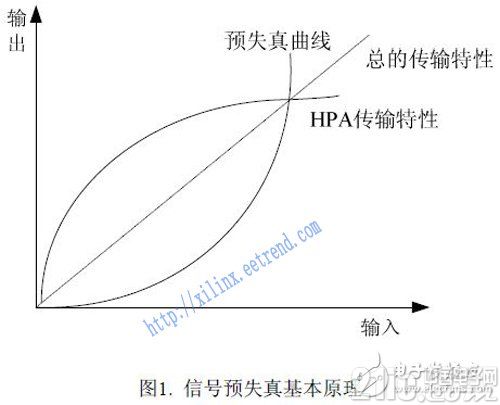

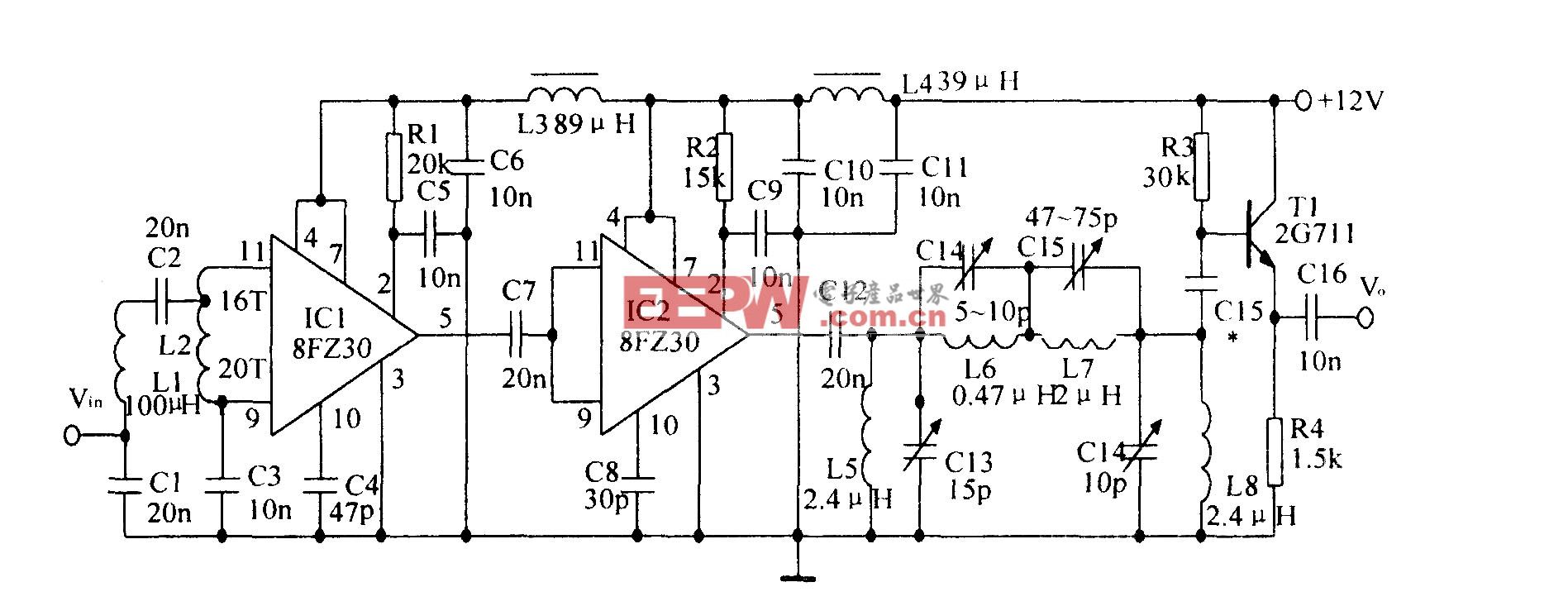

数字基带预失真是根据HPA的非线性失真曲线,找出其反向特性函数,对输入信号进行相反方向的预失真,这样通过HPA后的总的传输特性呈线性,基本原理如图1所示。

基带预失真的优点是:电路相对简单,经过精心的调整后,能达到很好的校正效果;稳定性强,处理带宽大,适合单载波和多载波系统,即与系统的调制方式无关;与HPA的类型无关[13];

基带预失真技术可以通过查询表方式来实现,即构造一个预失真查询表,根据查询表对输入信号进行实时处理,这种方法可以应用于任何增益波形图的功率放大器,线性化效果好,但是需要占用较大的存储空间。

3. 基于FPGA 的非线性校正方法的实现方案

有两种对OFDM基带信号实现非线性校正的方案。一种是基于FPGA,一种是基于DSP。基于FPGA方案的优点在于集成度高,而基于DSP在算法实现和调试方面更为方便[6]。因为中高端的FPGA支持软CPU内核(典型的如Nios),可以用高级语言(如C语言)进行非线性校正算法的编程和调试,所以我们采用基于FPGA的校正方案。

数字基带矢量信号通常分解为I(实部)和Q(虚部)两路正交分量信号的形式传输。

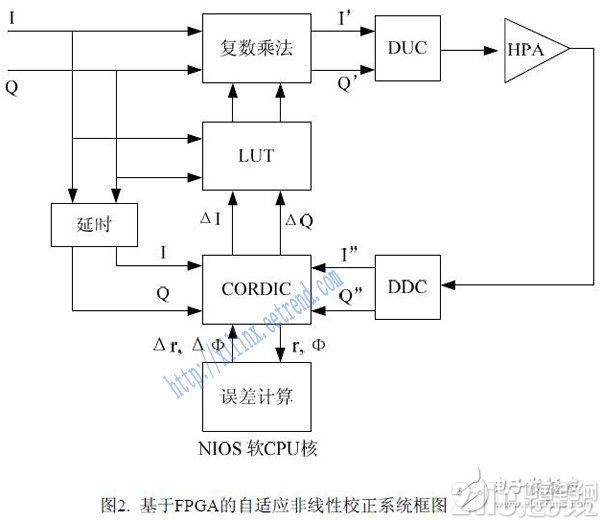

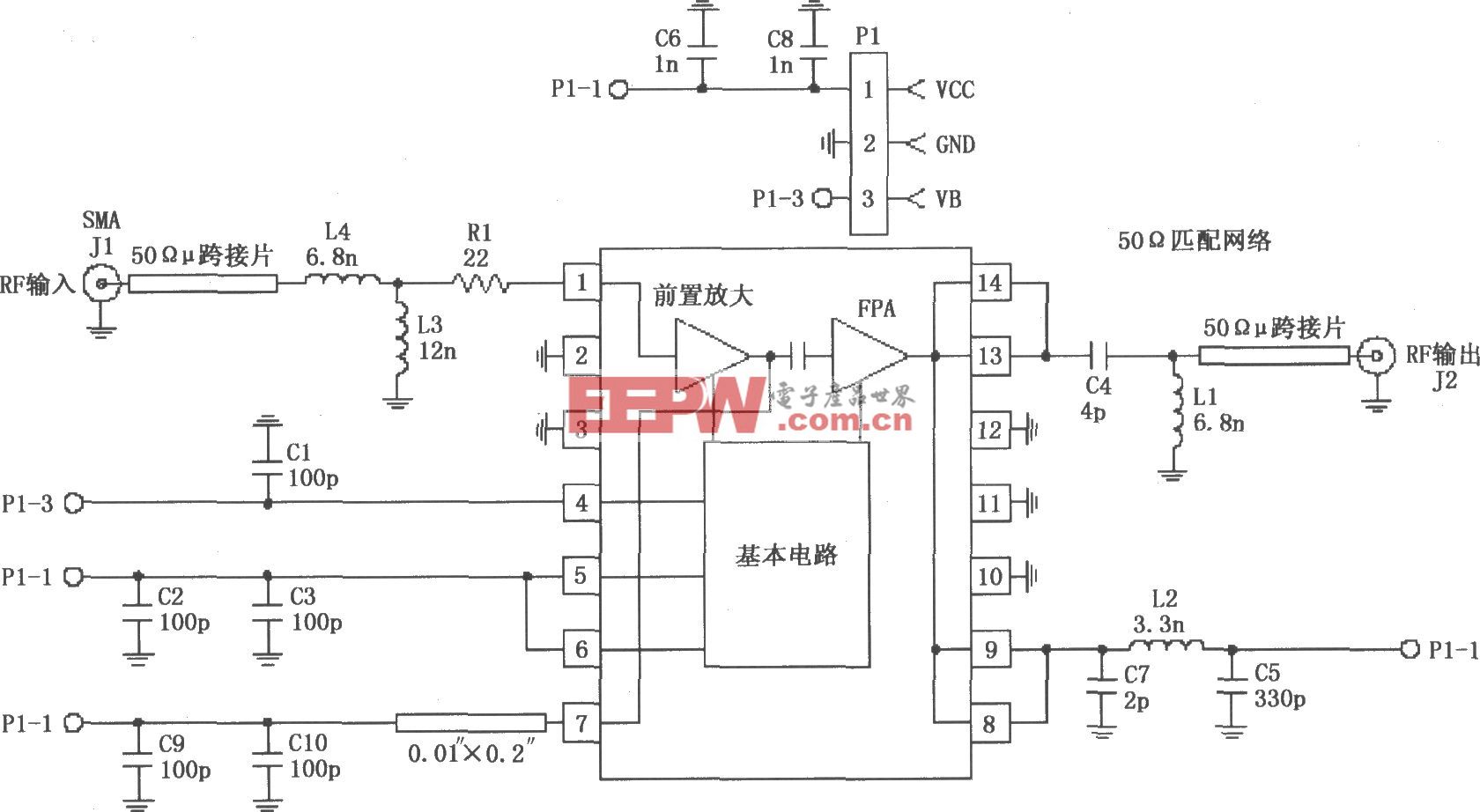

我们设计的基于FPGA的非线性校正方案的系统框图如下:

其中,I 'Q'为原始基带输入信号IQ经预失真后得到的信号,I ''Q''为射频解调后得到的基带信号。

本校正系统主要包括三个部分:

查找表模块:以输入信号功率值为索引,动态存储自适应预校正算法计算得到的复数值。原始输入基带信号与其对应索引项中的值进行复数乘法[4],即得到预失真后的基带信号。

CORDIC模块:完成直角坐标(实部和虚部)和极坐标(模值和相位)之间的转换。因为Nios软CPU内核算法是基于模值和相位(R*)的,而其它如查找表项值,输入信号和反馈信号的都是基于实部和虚部(IQ)的。该模块通过简单的移位运算和加减法运算就能完成直极转换,具有很高的计算效率[9]。

Nios软CPU内核及其自适应预失真算法,这是非线性校正系统的核心部分。Nios CPU是一种采用流水线技术、采用16位指令系统的单指令流RISC处理器,具有强大的寻址模式和良好的可扩展性,而且具备通用CPU的一般控制和运算功能,并可以根据性能需求由用户生成(用户定制),可获得较高的性能资源比。自适应预失真算法根据输入信号和反馈信号的差值信息(反映放大器特性因温度或老化发生变化)进行某种方式(如牛顿切线法)的迭代算法,逐次更新查找表,并经一定次数的迭代运算后趋于收敛。

方案实现时需注意的问题:

1. 关于同步控制

在生成预失真表时,必须保证是原始IQ与相对应的IQ进行比较,即同步控制。一般情况下,我们认为延时是固定的。可以通过特征序列来计算延时,也可定期用特征序列来更新延时。

2. 关于反馈延时电路的幅度调整

由于反馈信号同原始信号需要作比较,因此要对反馈信号作相应的衰减,将反馈信号和原始信号进行归一化的处理。可以依靠系统初始化过程中的特征序列确定对反馈信号的衰减值。

4. 结语

本文提出的基于Nios软CPU内核的FPGA非线性校正方案,具有集成度高、灵活性强、调试方便的优点,而且在DAB小功率实验发射系统中进行了实测,信噪比提高了12dB,非线性补偿效果较为理想。

评论