基于FPGA的三相正弦DDS电路的设计与实现

1. 引言

本文引用地址:http://www.amcfsurvey.com/article/201809/389161.htm直接数字频率合成器(DDS)技术,是根据相位的概念出发直接合成所需的波形的一种 新的频率合成原理,是一种把一系列数字形式的信号通过DAC转换成模拟形式信号合成技术。 具有频率切换速度快,很容易提高频率分辨率、对硬件要求低、可编程全数字化便于单片集 成、有利于降低成本、提高可靠性并便于生产等优点。目前各大芯片厂商都相继推出高性能 和多功能的DDS芯片,内部数字信号抖动很小,输出信号的质量较高。但是在某些场合,由 于专用的DDS芯片的控制方式是固定的,故在工作方式、频率控制等方面与系统的要求差距 很大,数字控制器接口不便,难以满足复杂要求,对处理速度要求较高,从而也限制了频率 进一步的提高,同时微处理器的处理任务也更加繁重。FPGA以其可靠性高、功耗低、 保密性强等特点,在电子产品设计中得到广泛的应用。

本文根据实际需要,设计出符合特定需要的三相正弦DDS电路,通过实验证明,利用FPGA 合成DDS是一个较好的解决方法,具有良好的实用性和灵活性。

2.正弦直接数字频率合成器设计原理

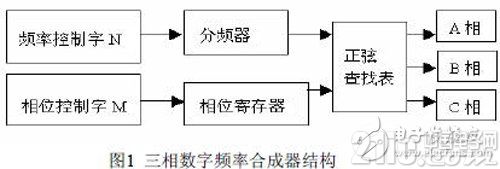

合成器由频率控制字N,相位控制字M分别控制输出正弦波的频率与相位。其中相位累 加器为合成器的关键控制部分,通过控制改变频率控制字N与相位控制字M的快慢,从而得 到相应频率和任意超前与滞后的相位的正弦波型,甚至是余弦波型。实际这种改变相位控制 字M与频率控制字N的配合,通过查找正弦表地址来得到。实际将每个地址对应正弦表中的0-360范围内的每一个相位点。查表将输入的地址信息映射成相应的幅值,从而得到完整的 正弦信号,同时通过数模转换器DAC,经过LPF(低通滤波器),就可以得到一个频谱纯净的 正弦波。其原理图如图1所示:

3.正弦波发生原理及逻辑设计

3.1 正弦函数表的设计

在传统正弦函数ROM 表的设计中,通常将0 到2π整个周期所有的离散信号全部存入芯片中[5]。这种方法虽然实现比较简单,但同时会浪费芯片的大量资源。

考虑到正弦波信号在0 到π与π到2π关于直线X=π成偶对称,故可以将ROM 表中的数据减少为原来的一半。再利用左半周期内,波形关于直线X=π/2 成奇对称,进一步可将正弦函数ROM 表减少一半。这样,就可以将ROM 表的数据减少为原来的1/4,可极大减少正弦函数ROM 表在芯片内部占用的逻辑资源。即通过一个正弦波形表的前1/4 周期,就可以变换得到正弦的整个周期波形,同时减少了将近3/4 的周期资源而使系统得到优化,效果非常显著。

根据以上思路,利用公式-1 提前把算好的正弦函数离散值,按照相应的地址顺序依次存入芯片内部的ROM 区中。本文的设计中采用以上思路,将0 到2π一个正弦周期内共有8192 个离散点,缩减为0 到πM2,共2048 个离散点,其中相位分辨率为0.044o。将N 作为正弦离散值的地址线,离散点的计算按公式-1 计算。

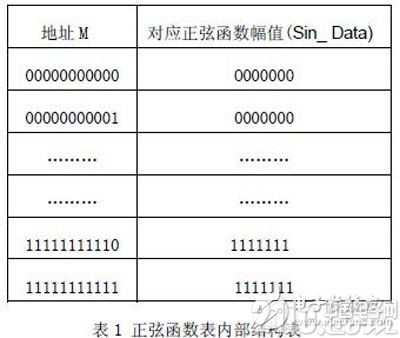

Sin_ Data=127mes;sin(π/2n) 其中n 的范围[0,2047] ---- 公式-1其中正弦表的内部结构如表1 所示:

3.2 三相正弦信号的产生原理

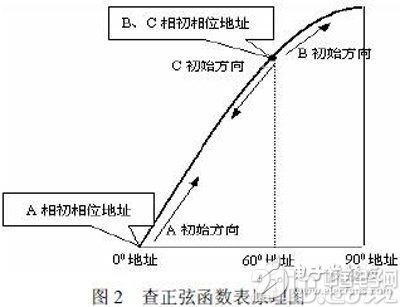

由于在设计中采用了一个正弦表,而需要产生三相正弦信号则成为逻辑设计的一个难点 与关键点。传统的设计中则需要在FPGA 内部存储三个正弦函数表,非常浪费芯片的逻辑 资源。因此,本文产生三相正弦信号利用了三相分时原理设计。在设计中采用三个可逆计数 器,分别在时钟信号的作用下同时进行计数,其计数值作为三相正弦信号在ROM 表中的地址。由于产生的三相正弦信号彼此的初相位不同,所以在可逆计数器的作用下,三个可逆计 数器的查表方向对于A、B、C 三相就各有所不同。其查正弦函数表原理如图2 所示:

例如在设计中产生三个初相位为零,相位互差120o°的三相正弦信号。如图2 所示,A 相首先从正弦函数表的地址0°开始累加读起,当读到地址90° 处,再从地址90°处累减读到 地址0°处,这样在A 相可逆计数器的控制下,就可以得到周期为π 的单向半波正弦信号;C 相首先从正弦函数表的地址60°开始递减读起,当读到地址0°处,再从地址0°处递增读到地 址90°处,然后从地址90°处递减读到地址0处,这样在C 相可逆计数器的控制下,就可以 得到周期为π ,初相位滞后A 相60°的单向半波正弦信号;同理B 相从正弦函数表的地址60o 开始累加读起,在B 相可逆计数器的控制下,就可以得到周期为π,初相位滞后C 相60°的 单向半波正弦信号。这样通过一个π/2 周期的正弦函数表,就可以发出三个相位互差60°周 期为π 的单向半波正弦信号。

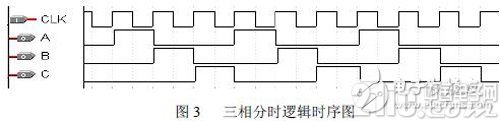

正弦函数表中读取对应的正弦幅值采用分时的方法。其中分时时钟非常小,在不影响正 常三相正弦信号的相位关系下,分相逻辑产生器产生的时序如图3 所示,其中CLK 为输入 系统时钟,分相逻辑产生器输出A、B、C 三个依次滞后的时序。当A 为高电平时读取从正 弦函数表内读取出A 相的正弦幅值;B 当为高电平时,读取B 相的正弦幅值;C 为高电平 时,读取C 相的正弦幅值。这样在三相分时逻辑控制器的作用下,将查出的三个单相半波 正弦信号送给正弦信号幅值调节器。

将三个单相半波正弦信号调整为周期为2π的正弦信号,利用公式-2、公式-3 就可以调节为正常的正弦信号。

3.3 相位的调节方法

M 作为相位控制字输入信号,将输入信号M 作为正弦函数ROM 表的偏移地址。当系统要 求发出超前参考信号的角度时,首先超前与滞后标志位变为“1”。可逆计数器查表地址从初 始位置对应偏移到ROM 表地址。如果M=“01010101011”(即δ=683 为相对偏移地址,实 际M=683? 0.0440=30o),A 相可逆计数器首先从地址“01010101011”处先递增计算,递增 到“11111111111”处就开始递减计算,计算到地址“00000000000”处再递增计算,在时钟 的作用下往复计算。B 相可逆计数器从地址1365+683 处(1365 为60° 地址)递减计数;同理C 相可逆计数器从1365+683 处递增计数。这样输出的正弦信号比参考信号超前30°。同 理.发出滞后电网电压信号的正弦信号只需采用与超前相反的方法。由于在正弦函数ROM 表 中存储了(0°-90°)的正弦函数值,共2048 个离散点,M 的调节范围在(-90 °—+90 °)之 间,相位分辨率为0.044°。

4 实验结果

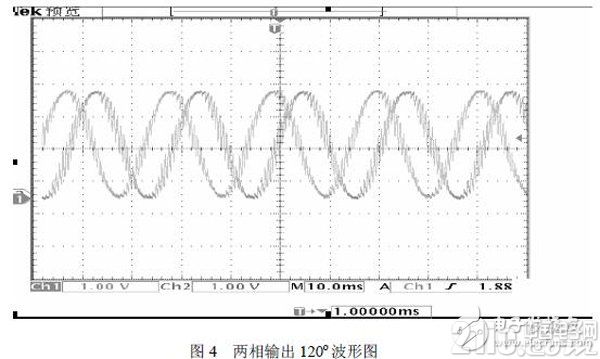

将编译好的配置文件下载到 FPGA 芯片中,用示波器来观测输出波形。为A 相与B 相LPF 滤波后的波形图图4,可以看出A 相与B 相彼此相位保持120o 的相位关系,证明输出三相波 形的相位是正确的。

在实际应用中,通过改变频率控制字的大小就可以改变输出频率。本文利用FLEX10K 器件,设计了相应的三相正弦DDS 电路,对实验电路进行了全面检验。实验结果表明:①整 体逻辑设计是正确的;②输出的三相波形相位符合设计要求的控制。

5.结束语

本文根据实际需要,设计出了符合特定需要的三相正弦DDS 电路,通过实验证明,输出 波形达到了技术要求,控制灵活、性能良好。 本文作者创新点:本文所做的研究是利用FPGA设计出符合特定需要的三相正弦DDS电路。 实验证明了该方法的可靠性和可行性。该方法较传统方法具有良好的实用性和灵活性,有很好的推广价值。

评论