关于PCB设计生产过程中如何抗ESD的问题,终于有答案了!

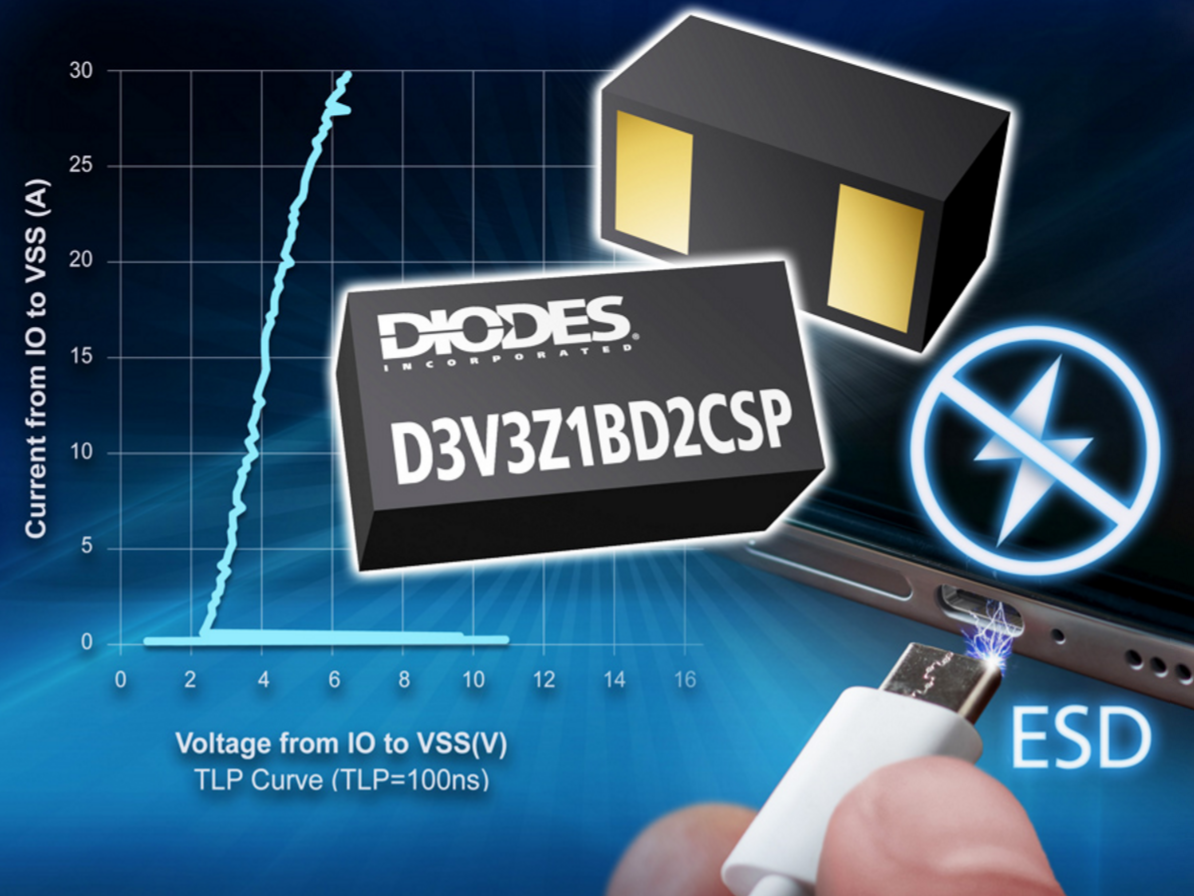

ESD(Electro-Static discharge),即静电释放。静电是自然现象,其特点是长时间积聚、高电压、低电量、小电流和作用时间短等。人体接触、物体摩擦、电器间的感应等,都会产生静电,电子产品基本上都处于ESD的环境之中。ESD一般不会直接损坏电子产品,但却会对其造成干扰,会导致设备锁死、信号干扰、数据丢失等。故此,电子产品必须做好抗ESD,PCB作为电子产品的基本器件,也不可忽视。

本文引用地址:http://www.amcfsurvey.com/article/201809/389075.htm那么,PCB在设计、生产过程中,应该如何抗ESD呢?给大家简单介绍:

首先在电路设计上,应当减少环路面积。因为环路具有变化的磁通量,电流的幅度与环的面积成正比,环路越大,则磁通量越大,则就能感应出越强的电流。故环路面积越小,能够感应到的静电电流越小。

其次,尽量使用多层PCB,因为多面PCB的地平面、电源平面、信号线、地线的间距可以减小工模阻抗和感性耦合,从而减少ESD。

第三,尽量使用较短的信号线,因为长的信号线可以接收ESD脉冲能量。尽量把每个信号层紧靠着相应的电源层或地线层。如果元器件比较密集,可以使用内层线。

第四,如果PCB周围画出不加组焊层的走线,可以将走线连接至外壳,但不能构成一个封闭的环,以免形成环形天线而引入更大的麻烦。

第五,可以采用有钳位二极管的CMOS器件或者TTL器件保护电路,有了钳位二极管的保护,在实际电路设计中减小了设计的复杂度。

评论