一个用于流水线模数转换器的高精度、低功耗采样保持电路

采样保持电路(S/H)是数据采集系统尤其是模数转换器(A/D)的一个重要组成部分。近几十年来无线通讯的迅速发展,使得数据的传输速率越来越快。复杂度不断提高的调制系统和电路使得模数转换器(ADC)的采样频率达到射频的数量级,与此同时,模数转换器的精度也超过12位以上。在这种高速度和高精度的要求下,采样保持电路的作用就越发显得重要,因为它可以消除模数转换器前端采样级的大部分动态错误。传统的开环采样保持电路只能达到8~10位的精度,主要由于开关的非理想特性,诸如电荷注入、时钟馈通、开关的非线性电阻等。

本文引用地址:http://www.amcfsurvey.com/article/201809/389005.htm另一方面,高精度的闭环采样保持电路又受限于运算放大器的性能。无线通讯系统十分重视降低功耗,流水线A/D通常是无线通讯器件中的一部分,因此在设计的时候也将功耗作为一个重要的考虑因素。本文设计了一个用于14位20MHz流水线A/D的采样保持电路,通过采用flip-around结构来降低功耗。同时为了抑制传统开关的一些非理想特性,采取自举开关来降低信号失真,从而提高整个系统的信噪比。通过采用增益增强技术,实现了高增益低功耗运算放大器。通过这些措施,在较低功耗的情况下仍然获得了14位的精度。

本文主要分以下几部分:介绍采样保持电路的结构;详细介绍运算放大器的设计;描述自举开关的实现;最后给出电路的仿真结果和结论。

采样保持电路的结构

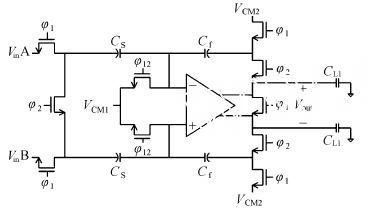

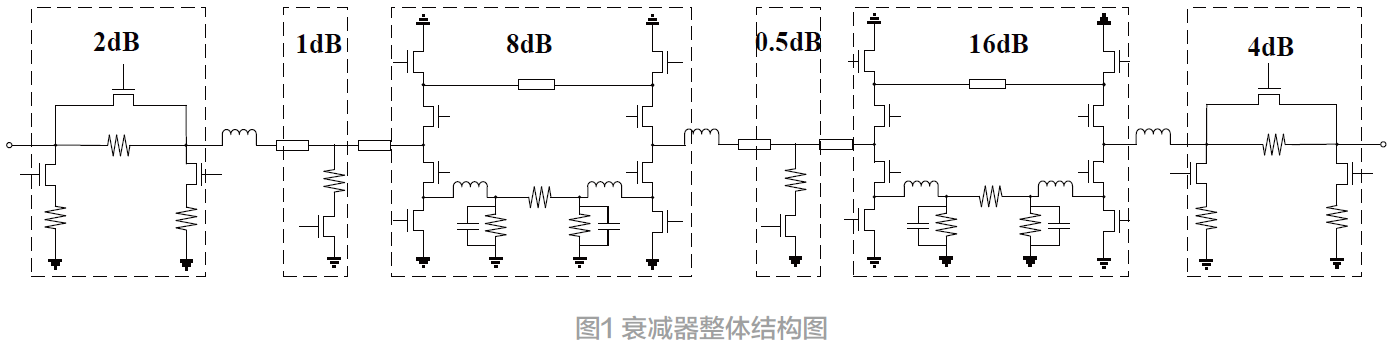

采样保持电路的要求主要是在较低功耗的情况下能采样大带宽、高频率输入信号,并且在驱动较大负载的情况下实现尽可能小的失真。闭环转换电容采样保持电路通常有两种结构,如图1和图2所示。

图1 电荷传输结构采样保持电路

图2 Filp-around结构采样保持电路

图1所示的结构称之为电荷传输采样保持电路(charge-transferringS/H)。在采样阶段,将输入信号存储在采样电容CS上,并且在保持阶段,仅将差分电荷转移到反馈电容Cf上。因为共模电荷存储在采样电容CS上,所以这种结构的采样保持电路可以处理共模范围较大的输入信号。

图2所示的结构称之为翻转(flip-around)采样保持电路。在采样阶段,将输入信号存储在采样电容C上,而在保持阶段,将采样电容C翻转到输出端。因此,理想的反馈因子β,第一种结构为0.5,而后一种在忽略输入管的寄生电容情况下为1,后者的反馈因子是前者的两倍。因此在同样的闭环带宽要求下,后者的放大器单位增益带宽(GBW)只需要前者的一半,这就大大地降低了放大器的功耗。而采样保持电路的功耗主要来自于内部运算放大器的功耗。

对于A/D而言,采样保持电路的输入噪声直接影响到A/D的输入参考噪声。因此要尽量减小由采样保持电路引入的噪声。在采样阶段,忽略晶体管的寄生电容,则电荷传输采样保持电路的输入参考噪声功率为V2n=(2κT)/C。而翻转采样保持电路的输入参考噪声功率为V2n=κT/C。后者的噪声比前者降低了一半。在保持阶段,假设放大器的噪声主要由输入晶体管的热噪声决定,则输入参考噪声功率可以用公式表示:

V2n=(8πκT)P3βCL[1] (1)

(1)式表明翻转采样保持电路由于较高的反馈因子使得噪声功率仅为电荷传输采样保持电路的1/2。

由于在减小噪声和降低功耗方面的优势,采用翻转结构作为采样保持电路结构。但需要指出的是,由于输入晶体管寄生电容的影响,使得反馈因子小于理想值1,所以在噪声和功率方面的改进可能会小于上面的理想值。另外,如果输入信号的共模电压V sig-cm不等于采样保持电路中运算放大器的输出共模电压V out-cm,则在维持阶段,由于运算放大器的共模反馈电路使得输出的共模电压稳定在V out-cm,因此运算放大器的输入共模电压会有一个阶跃变化ΔV in-cm=V out-cm-V sig-cm。因此为了满足各种共模信号的要求,则该运算放大器要求较大的输入共模范围。

运算放大器的设计

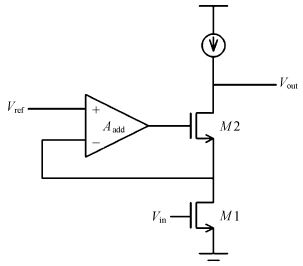

由于噪声和功率方面的优势,采用翻转结构作为采样保持电路的结构,同时采用折叠式共源共栅放大器来实现大输入共模范围的要求。采用PMOS管作为输入管,这样就可以使第二个极点推到较高的位置。因为,第二个极点的位置为折叠点。而NMOS折叠管的寄生电容比PMOS折叠管的寄生电容小的多。除此之外,PMOS管还可以采用自衬底工艺,从而大大减小由于工艺产生的偏差。唯一的缺点是PMOS输入管有较大的寄生电容,从而减小翻转结构在功率和噪声方面的改进。

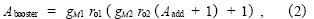

另外由于该采样保持电路运用于14位20MHz流水线A/D,则要求该放大器的直流增益必须大于93dB,输出在25ns的建立时间内稳定在最终值0.003%。对于单极点放大器,建立时间又可以转化为对GBW的要求。因此为了实现近似单极点放大器,则要求放大器必须为一级结构。而为了实现如此高的直流增益,则必须采用增益增强技术,原理示意图如图3所示。图中,由M1、M2和理想电流源构成主运放,Aadd为用于增益增强的辅助放大器。采用该技术后,这个电路的直流增益为:

其中,ro1、ro2为M1、M2的输出电阻,gM1、gM2为M1、M2的跨导。

图3 增益增强结构的运算放大器

采用该技术之前,放大器的直流增益为:

(2)式和(3)式表明,增益增强技术可以使放大器的直流增益提高一个数量级。因此在该放大器的设计中,采用如图4所示的带有A1和A2两个辅助放大器的增益增强折叠式共源共栅放大器,其中,A1和A2以外的部分为主放大器。为了简化设计,辅助放大器也采用折叠式共源共栅结构。因此,辅助方法器和主放大器的偏置电路可采用同一个偏置电路,大大简化了设计。而辅助放大器的电流仅为主放大器电流的1/10,因此与套筒式共源共栅放大器相比,整体电路并不会额外增加电流。

图4 增益增强折叠式共源共栅运算放大器

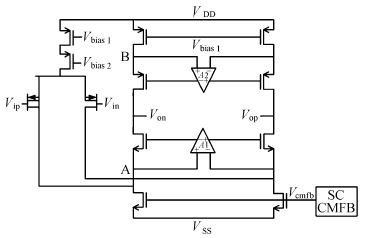

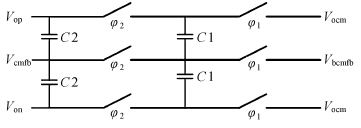

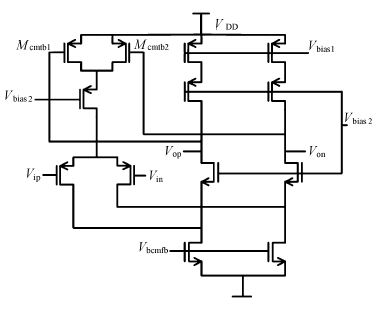

需要提出的是,主放大器和辅助放大器采用了不同的共模反馈电路(CMFB)。对于主放大器而言,因为输出电压范围2Vpp,因此在实现较大的输出摆幅,又不额外增加功耗的要求下,采用开关电容共模反馈电路。如图5所示,通过电容C1和C2间的电荷转移调节电流源管的栅电压来改变输出电流,从而稳定输出共模电压。对于辅助放大器而言,其输出摆幅很小,输出为共栅管的偏置电压,采用一种简单的连续时间共模反馈电路,如图6所示,其原理是通过调节Mcmfb1和Mcmfb2管子的电流来稳定输出共模电压。

图5 开关电容共模反馈电路

图6 辅助放大器及其共模反馈电路

自举开关

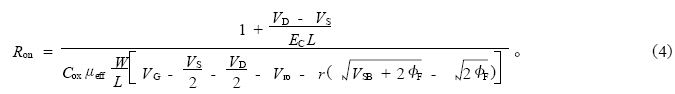

开关是采样保持电路的一个重要组成部分。它是信号失真,电荷注入和时钟馈通效应主要来源。后两者可通过采用下极板采样和全差分电路结构来消除。A/D对信号失真要求很高,因为失真直接影响到A/D的精度。当信号幅度较高时,采样保持电路的精度和速度就直接受限于失真。而失真的主要原因是开关导通电阻的非线性。开关导通电阻不是一个固定值,而是输入信号的函数。对于短沟器件的导通电阻为:

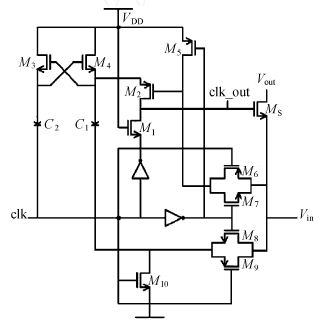

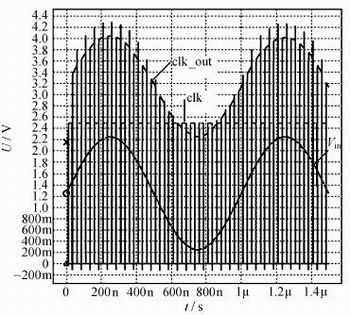

其中VG,VS,VD和VB分别为晶体管栅、源、漏和衬底电压。一般,输入信号电压连接在源端。假设,VS=VD=VB。通过PMOS管的自衬底技术使衬底和源短连接在一起,从而消除分母中后半部分平方根中的部分。则开关的导通电阻RON主要有VG-VS的差值决定,自举开关就是通过固定这个差值来实现开关的线性导通电阻,从而消除信号失真。自举开关电路如图7所示,工作原理是:当CLK为高的时候,自举开关属于关断状态,此时开关MS的栅通过管子M1连接在VSS。而同时,电容C1两端电压差为VDD-VTH,其中VTH为NMOS管的阈值电压。当CLK为低的时候,自举开关属于导通状态,此时,M1管关闭,通过M2管使开关MS的栅电压固定为Vin+(VDD-VTH)。其仿真结果如图8所示。需要指出的是,图2中4处有开关,其中S1和S2采用自举开关,S3采用CMOS传输门,S4采用简单NMOS传输门,这样可以简化电路并降低功耗。

图7 自举开关

图8 自举开关仿真结果

仿真结果和结论

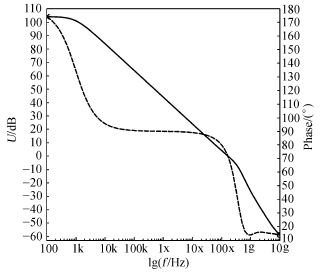

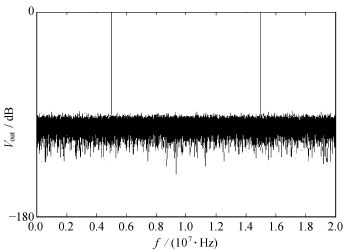

图4所示的运算放大器的Hspice的仿真结果为图9,在电路负载为15p的情况下,直流增益为104.6dB,单位增益为166MHz,相位裕度为71度。完全满足设计要求。图10为该采样保持电路的在输入信号为5MHz,全差分信号幅度为2Vpp采样频率为20MHz情况下的输出频谱图。仿真结果显示,该电路的SFDR为92.4dB,SNDR为88.6dB,SNR为96.1dB。

本文描述了一个用于14位20MHz流水线A/D的采样保持电路。该电路采用UMC logic 0.25μm2.5V工艺,通过采用增益增强放大器和自举开关,在输入为±1V频率为5MHz正弦波,采样频率为20MHz的情况下获得了96.1dB的信噪比。

图9 运算放大器的频率特性曲线

图10 仿真频谱图(fin=5MHz,fs=20MHz)

评论