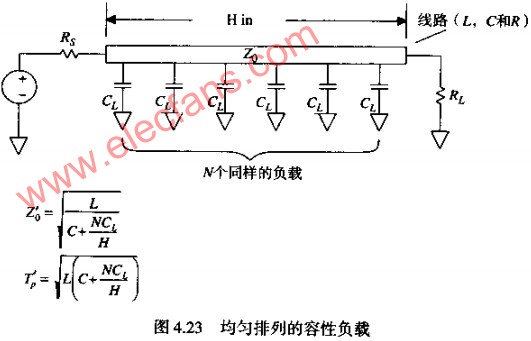

等间隔的容性负载

图4.23中的情形,经常出现在大的总线结构中,尤其是在包含大的单排存储模块囝列的存储卡上。容性负载的值相等而且间隔均匀地排列。

本文引用地址:http://www.amcfsurvey.com/article/201809/388867.htm

如果上升沿的长度超过了负载间的距离,则可以推导出这个电路特性的一个简化的近似表达式。这个近似表达式将会告诉我们两件事:

1)线路的有效阻抗被减小。

2)线路的传播延迟增加。

这两项都严重地影响了高速信号总线的性能。

1、均匀负载总线的有效阻抗

由于上升沿的有效长度与负载间隔相当,按照式( )信号将来回地反弹。对于非常轻的负载,只需分别把每个负载的反射累加起来,就可以计算出总的反射脉冲高度。这些反射信号的总和是一个最坏的运行情况,因为反射脉冲不会同一时间全部到达上任何一点。

)信号将来回地反弹。对于非常轻的负载,只需分别把每个负载的反射累加起来,就可以计算出总的反射脉冲高度。这些反射信号的总和是一个最坏的运行情况,因为反射脉冲不会同一时间全部到达上任何一点。

第二次和第三次的反射衰减严重,因而通常不值得进行计算。

对于上升沿长度大于负载间隔的情况,每个电容的影响平均地分布在上升沿的边上,如果我们采用两倍数量的电容,而电容的值减小一半,或者是将电容的容量以相等的比率均匀地分布到线路上,产生的效果将没有什么不同。

电容均匀地分布地理解这个电路的关键。

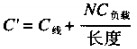

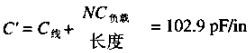

构造一个新的传输线模型,每英寸具有电感和阻抗与原传输线相同,但有一个新的电容,总负载电容除以总路线长度的英寸数,得到每英寸的负载电容。然后用这个电容值加上传输线原有的每英寸电容,得出新模型的电容:

其中,C负载=负载电容,PF

N=负载数量

长度=总线长度,IN

C线=传输线的电容,PF/IN

C=新模型的有效电容,PF/IN

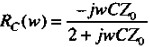

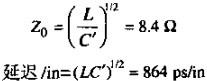

现在利用这个模型,可以重新计算有效传输线阻抗Z:

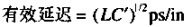

2、一个均匀负载总路线的传播延迟

其中,C=新模型的有效电容,PF/IN

L=原有电感,PH/IN

例:均匀负载的总路线

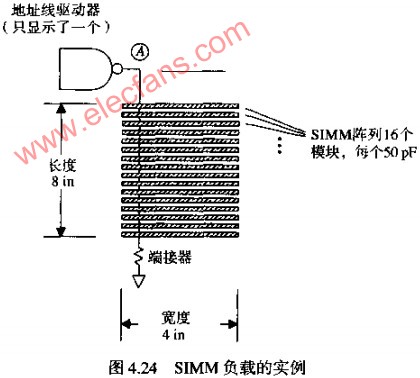

SAM将用SLMM模块构造一个大的存储电路板,他计划用16个SIMM组成一个大存储器阵列,如图4.24所示。所有16个SIMM的地址线并联在一个驱动端,记为门电路A,这里是每条线的临界参数:

C负载=50PF

N=16

长度=8IN

C线PF/IN

L=7250PH/IN

首先计算沿线的有效电容:

用新的电容值重新计算ZO和传播延迟:

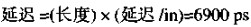

总的线路延迟是:

在第一个SIMM之后6.9NS,最后一个SIMM才接收到地址数据,这个偏移将降低存储器的定时裕量,不仅如此,端接值和驱动阻抗都不得不非常低。

可能的解决办法都涉及将SIMM地址总路线分为多条总线,每条总路线上只有少数几个负载。

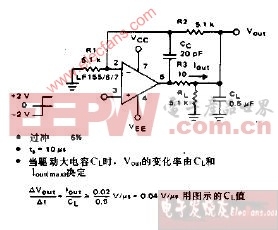

做为一个检验,SAM应该使用与图1.6中类似的电路来测量总的线路电容(C*长度)。SAM可能需要使用比图1.6中更小的电阻,以提供驱动SIMM输入端在其跳变范围所需的电流。

评论