给MCU工程师详解FPGA硬件属性

我的许多朋友都是经验丰富的嵌入式设计工程师,但他们都是微控制器(MCU)背景,因此对于FPGA是什么以及FPGA能做什么只有一个模糊的概念。如果问急了,他们会说“你可以通过配置FPGA让它做不同的事情”诸如此类的话,但他们真的不是很清楚FPGA里面有什么,或者如何在设计中使用FPGA。

本文引用地址:http://www.amcfsurvey.com/article/201808/386541.htm事实上,MCU对有些任务来说是很适合的,但对其它一些任务来说可能做的并不好。举例来说,当需要并行执行大量计算任务时,FPGA可能会让你喜出望外。在本文中我们将讨论FPGA的硬件属性。

简单的FPGA构造

在集成电路领域人们经常会听到构造(fabric)这个术语,它指的是FPGA器件的底层基础结构。(作为一个兴趣点,单词“构造”来自中世纪英语fabryke,意思是“建造的某些东西”)。下面让我们从FPGA中的内核可编程构造开始吧……

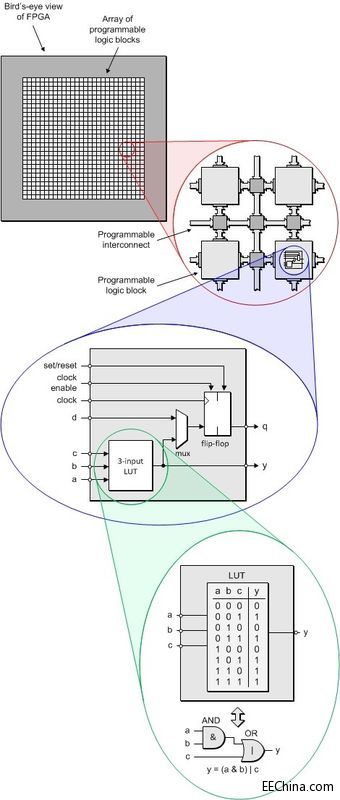

如果我们仔细观察FPGA封装的内部,我们将看到硅片(技术术语裸片)。可编程构造表现为可编程逻辑块阵列,如下图所示。如果我们用放大镜“放大查看”,我们可以看到这种构造由沉浸于可编程互连“海洋”中的许多逻辑“岛”(可编程逻辑块)组成。

图1:简单的FPGA构造。

基本FPGA可编程构造的一般性表示。

是啊,我确实是用自己的双手亲自创作的这幅图片,我因此感到非常自豪呢,非常感谢你加以关注。如果我们进一步放大,我们可以看到,每个可编程模块都包含有许多数字功能。在这个例子中,我们可以见到一个三输入的查找表(LUT)、一个复用器和一个触发器,但重要的是我们要认识到,这些功能的数量和类型对不同系列的FPGA来说是会变化的。

触发器可以被配置(编程)为寄存器或锁存器;复用器可以被配置为选择一个到逻辑块的输入或LUT的输出;LUT可以被配置为代表任何所要求的逻辑功能。

更详细地了解LUT

上面所示的简单例子包含一个三输入的查找表(LUT)。在实际应用中,即使最简单的FPGA都会使用四输入LUT,而一些更大更复杂的器件甚至会宣称使用六、七或八输入的LUT,但为了简单起见,我们还是讨论三输入版本。

我们会在以后的文章中讨论各种类型的FPGA实现技术。现在我们只需要知道,FPGA内部的可编程单元可以用反熔丝、闪存单元或SRAM内存单元来实现。先让我们看一个用反熔丝技术创建的FPGA吧。这是一种一次性可编程(OTP)技术,这意味着一旦你编程了这个FPGA,它将永远保持这个状态而不再改变。

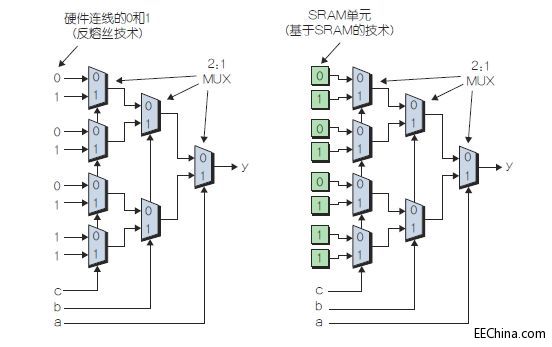

形象化介绍这种技术的最简单方法是用下图所示级联的2:1复用器(MUX)。对基于反熔丝技术的FPGA来说,编程器件相当于通过“硬件连线”将第一组复用器的输入连接到实现目标逻辑功能所需的正确0或1值。下图中所示的值反映的实际结果是,我们使用这个LUT实现了前面那张图隐含的公式y=(a b)|c。在实际应用中,复用器可以用场效应管的分支“树”来实现,但我们在这里真的不用担心最底层的实现细节。

图2:输入值经“硬件连接的”反熔丝型LUT(左),输入从SRAM单元馈入的SRAM型LUT(右)。

另外一种非常常见的FPGA实现技术是使用SRAM配置单元。同样,我们会在以后的文章中讨论更多的细节。这里我们所要知道的仅是当电路板第一次上电时,基于SRAM的FPGA会加载配置信息(我们可以把这个过程想像为器件的编程)。作为这种配置的一部分,用作LUT复用器输入的SRAM单元会被加载进上图所示的目标0或1值。

我没有显示0和1被加载进SRAM单元的那种机制,因为我不想让问题变得复杂。出于这次讨论的目的,我们真的无需担心这种“魔术”是如何发生的。我在这里唯一要提的事(给你考虑的空间)是—使用一种被称为部分再配置的技术—FPGA的一部分可以发起对另一部分进行再配置(当然反过来也行)。对于具有微控制器和/或软件背景的读者来说,我们可以将这种技术想象为相当于自我修改代码的硬件。这意味着这种技术是非常非常强大的,但也会带来很难隔离和调试的问题。

通用的输入和输出

FPGA器件还包含有通用的输入/输出(GPIO)引脚和焊盘(图1中没有显示)。通过配置单元,FPGA器件内的互连部分可以被编程为这样:将器件的主输入连接到一个或多个可编程逻辑块的输入。任何逻辑块的输出也可以用来驱动任何其它逻辑块的输入和/或FPGA器件的主输出。另外,GPIO引脚可以被配置为支持种类广泛的I/O标准,包括电压、终端阻抗、摆率等。

世界上第一块FPGA与本文中讨论的架构非常类似。这块FPGA就是赛灵思公司在1985年推出的XC2064(是用2um工艺节点制造的),它包含有8×8=64的逻辑块阵列,每个逻辑块包含一个四输入LUT和其它一些简单功能。从那以后,FPGA发展势不可挡,正像我们看到的那样……

更为复杂的FPGA架构

正如我们在前面说的那样,赛灵思公司在1985年推出的第一块FPGA—XC2064包含8×8=64的逻辑块阵列,每个逻辑块包含一个四输入查找表及其它一些简单功能。由于它们的容量非常有限,因此早期的FPGA只用来执行一些相对简单的任务,比如集中一些胶合逻辑,或实现基本的状态机。然而随着时间的推移,事情开始改变……

随着时间的推移和工艺节点的进步,FPGA的容量和性能不断得到提高,功耗却不断的下降。直到大约2006年以前广泛使用的一直是四输入查找表。事实上,在写这篇文章之时,较小的FPGA系列器件仍在使用四输入的查找表,但一些高端器件可能使用六、七或八输入的查找表。这些大家伙可能被用作一个大的查找表,或分裂成许多更小的功能,比如两个四输入的查找表或一个三输入一个五输入的查找表。在实际的高端器件中,这种可编程构造可以描述相当于百万级(有时甚至千万级)的原始逻辑门。

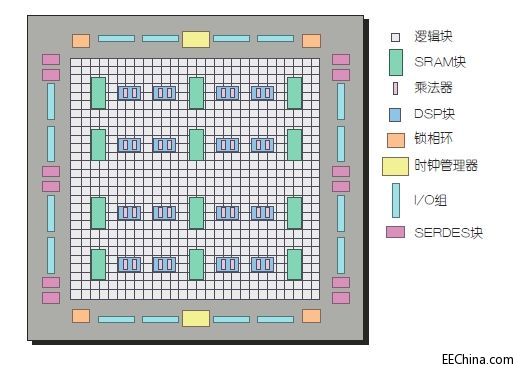

如果某个逻辑功能(比方说计数器)是用FPGA的可编程构造实现的,那么这个功能可以被说成“软功能”。相比之下,如果某个功能是直接用芯片实现的,则被说成“硬功能”。(随着这些功能变得越来越大越来越复杂,我们一般称它们为内核)。软内核的优势在于,你可以让它们做你想让它们做的任何事。硬内核的优势是它们占用较少的硅片面积,具有较高的性能,并且功耗较低。最优的解决方案是混合使用软内核(用可编程构造实现)和硬内核(直接用硅片实现)。这样,除了基于查找表的可编程构造外,今天的FPGA可以利用以下介绍的各种硬内核进行性能增强:

图3:更复杂的FPGA架构。

举例来说,该器件可能包含数千个加法器、乘法器和数字信号处理(DSP)功能;数兆位的片上内存,大量的高速串行互连(SERDES)收发器模块,以及众多的其它功能。

带嵌入式处理器的FPGA

这是真正让人兴奋的事情……你可以用FPGA中的普通可编程构造做的事情之一是,使用其中的一部分实现一个或多个软处理器内核。当然,你可以实现不同规模的处理器。举例来说,你可以创建一个或多个8位的处理器,加上一个或多个16位或32位的软处理器—所有处理器都在同一器件中。

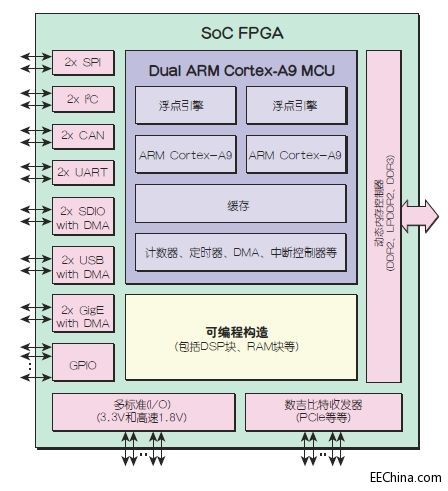

如果FPGA供应商希望提供一个占用较少硅片面积、消耗较低功率但性能更高的处理器,解决方案是将它实现为硬内核。一个非常令人兴奋的开发成果是Altera和赛灵思等公司最近推出的SoC FPGA。考虑下面所示这个例子:

图4:一种新的SoC FPGA

这个漂亮的小东西整合了一个完全以硬内核方式实现的双路ARM Cortex-A9微控制器子系统(运行时钟高达1GHz,包含浮点引擎,片上缓存,计数器,定时器等),以及种类广泛的硬内核接口功能(SPI,I2C,CAN等),还有一个硬内核的动态内存控制器,所有这些组件都利用大量传统的可编程构造和大量的通用输入输出(GPIO)引脚进行了性能增强。(即将在16nm节点推出的一款SoC FPGA据称包含四内核的64位ARM Cortex-A53处理器,双内核32位ARM Cortex-R5实时处理器,以及一个ARM Mali-400MP图形处理器。这些可不是你祖母时候的FPGA哦!)

传统的嵌入式系统架构师可能将其中一个器件放置在电路板上,并将它用作传统的高性能双内核ARM Cortex-A9微控制器。当电路板上电时,硬微控制器内核立即启动,并在任何可编程构造完成配置之前就可用了。这样可以节省时间和精力,并让软件开发人员和硬件设计师同时开始开发。

一种情形是软件开发人员捕获他们的代码,在SoC FPGA的Cortex-A9处理器上运行这些代码,然后通过分析识别任何可能严重影响性能并成为瓶颈的功能。这些功能随后可能就转交给硬件设计工程师用可编程构造来实现,它们(这些功能,不是设计工程师)将使用较低的时钟频率提供明显更高的性能,而且功耗更低。

前面我们说过,硬内核实现的功能(图4所示的ARM Cortex-A9就是一种硬内核)与等效的软内核相比具有更高的性能和更低的功耗。但现在我们又说如果在硬内核处理器上运行的软件功能是个瓶颈,我们可以用可编程构造来实现,这样它就能……你理解的没错,提供更高的性能和更低的功耗。

评论