基于DSP的SoC芯片的FPGA验证方法

3.1 DSP 核的验证

通过CCS界面对DSP内部寄存器进行读写操作并在CCS界面观测DSP内部寄存器的变化实现验证DSP的功能。分别对DSP内部 的Timer、GPIO、中断寄存器等进行读写及功能验证,并通过DSP控制其他各类寄存器以验证DSP核的正确性。

3.2 EMIF及片上储存设备的验证

利用DSP能够正确读写片上存储器设备及支持各类读写操作,对片上存储设备进行验证。为了验证EMIF接口,在FPGA工程里对EMIF I/O 口进行绑定约束使其与SRAM存储器子板进行正确的连接,通过DSP对EMIF空间寄存器的控制,使DSP能够正确地对连接在EMIF外的SRAM进行各类型的读写操作,可验证EMIF接口设计。

本SoC系统中设计的EMFI接口模块可以连接4个外部存储空间CE0~CE3。通过ISE工具使用 XILINX V6芯片的FPGA IP core例化4个宽度为32bit、深度为64的SRAM,并且将它们连接到CE0~CE3空间接口上。在CCS中,初始化CE0~CE3空间接口,对各空间前16个地址写数据,之后对这些地址进行读操作。执行单步调试命令,可以成功读取CE0~CE3空间地址里面写入的数据。DSP核指令代码,首先配置全局控制寄存器,选择DSP提供的系统时钟,指令代码写全局控制寄存器:*(int*)0x4000a000 = 0x00000000;配置CE0~CE3时钟寄存器和CE0~CE3空间寄存器:

*(int*)0x4000a004=0x00000004;*(int*)0x4000a008=0x00000006;

*(int*)0x4000a00C=0x00000008;*(int*)0x4000a010=0x0000000a;

*(int*)0x4000a014=0xffffffe6;*(int*)0x4000a018=0x1091c226;

*(int*)0x4000a01c=0x30d5c846;*(int*)0x4000a020=0x2251c736;

对各空间前16个地址写数据,之后对这些地址进行读操作的DSP核指令代码:

for(i=0;i16;i++)

{

*(int*)(0xC0060000+4*i) = (0x00000600+i);

*(int*)(0xD0060000+4*i) = (0x00000700+i);

*(int*)(0xE0060000+4*i) = (0x00000800+i);

*(int*)(0xF0060000+4*i) = (0x00000900+i);

}

for(i=0;i16;i++)

{

temp_data = *(int*)(0xC0060000+4*i);

temp_data = *(int*)(0xD0060000+4*i);

temp_data = *(int*)(0xE0060000+4*i);

temp_data = *(int*)(0xF0060000+4*i);

}

运行DSP核指令代码,观察CE0~CE3寄存器的值,能够成功进行读写,验证EMIF正确。

3.3 事件捕获、看门狗等功能模块的验证

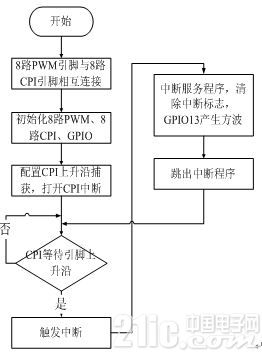

通过DSP操作控制看门狗逻辑模块寄存器,看门狗能够正确运行,并能够正确影响复位模块以验证看门狗IP模块。通过DSP正确操作CPI等寄存器,使CPI模块产生中断送至DSP,并且DSP能够正确响应中断信号进行及时处理。为了可方便验证CPI功能,此SoC验证CPI模块把PWM产生波输入到CPI模块,配置CPI捕获模式,当CPI模块输入有变化时,进行捕获产生中断。当发生中断时CPI_INT为高电平,当DSP处理后会变为低电平信号。验证方法原理如图4

图4 验证CPI模块原理框图

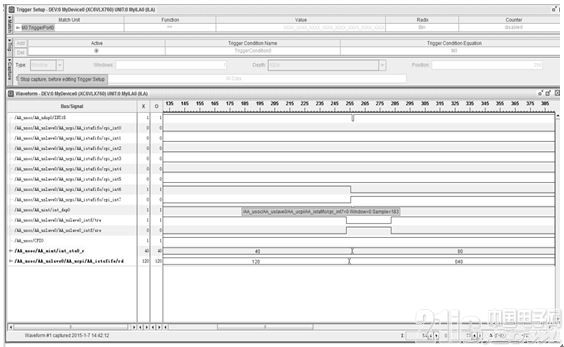

在ChipScope中正确设置触发条件并可以通过FPGA编程器及JTAG传送到PC主机,可观察其逻辑波形的正确性。下图5可以看车CPI_INT6从高电平到低电平的转化,可说明DSP对CPI中断事件进行了处理,并正确相应外部中断。可验证正确设置CCS配置IP模块寄存器后,IP硬件模块能够正常运行。

图5 CPI中断事件

3.4 PWM、SPI、CAN、UART等外设模块

通过控制内部寄存器,能够产生正确的PWM波,分别在示波器及ChipScope上对一些信号进行采取及观测分析,验证其正确性。验证方法和如上验证CPI、EMIF相同。测试验证结果表明其功能正确。其中结合示波器测试PWM波,验证PWM设计正确性。另外使用相同方法验证SPI、CAN、UART等各IP功能。

4 结论

本文基于一个DSP处理器控制的SOC芯片的开发与验证项目为基础。介绍了关于FPGA的软硬件协同验证方法及过程,搭建FPGA验证硬件平台及软件平台环境, 并通过软硬件协同验证, 在线验证调试SOC系统中逻辑及功能设计, 并对每个功能模块进行了验证分析。通过CCS输入控制DSP程序进而控制SOC系统及内部IP模块,具有可观测性及实时性,结果表明通过FPGA软硬件协同验证系统可以对目标SOC芯片进行功能验证及性能评估。缩短了基于SoC芯片的应用系统的开发时间,提高流片成功率。整个验证平台及方法具有较高的可靠性。

评论