如何基于EMIF接口的DSP控制系统设计?

摘要:提出一种DSP 通过EMIF 接口控制复杂系统的方案。通过将DSP 芯片连接多片FPGA,并利用FPGA 与各种外部芯片连接,使得DSP 通过EMIF 接口就能控制各种芯片,实现复杂系统的控制。这样节省DSP 的引脚资源,使DSP 的运算功能得以更充分的发挥。

本文引用地址:http://www.amcfsurvey.com/article/201808/385890.htm1 引言

随着信息技术的发展,数字信号处理技术成为数字化社会最重要的技术之一。由于数字信号处理器(DSP)速度快,稳定性高,功耗小,近些年来在通信、图像处理、自动控制等领域中得到了广泛的应用。其中,美国德州仪器公司(TI)的TMS320 系列DSP 占据了世界DSP 市场的主要份额,TI 也因此成为了世界上最大的DSP 制造商。本系统采用了TMS320C6722 浮点型DSP芯片。

EMIF接口(External Memory Interface)是TMS320 系列DSP上具有的一种高速接口,其设计初衷是实现DSP 与不同类型的外部扩展存储器(如 SDRAM,FLASH 等)之间的高速连接。在当前的一些应用中,为了更充分的应用DSP的运算能力,扩展其引脚资源,工程师们常用EMIF接口连接FPGA,再通过FPGA与多种外部设备相连。这样,FPGA成为了一个中转站,各种数字芯片的数据都可以通过FPGA传输至DSP.对于更加复杂的系统,当一块FPGA 芯片的引脚资源都被用尽时,可以在DSP 的EMIF接口上连接多块FPGA芯片,再将功能各异的芯片连接至FPGA.这样,DSP 芯片仅通过EMIF 接口就能实现对复杂系统的控制。

2 基于EMIF 接口的DSP+FPGA 系统实现

2.1 系统架构

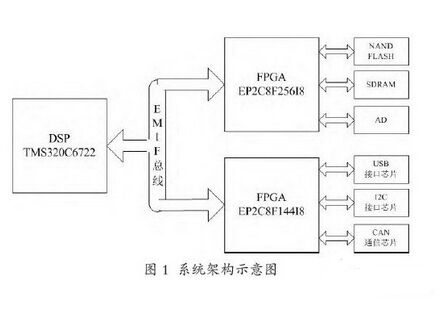

图1 是本人所使用的系统,DSP芯片通过EMIF接口连接了2 片FPGA,其中EP2C8F256I8 主要负责DSP核心处理所需数据的交换,连接了FLASH 芯片,SDRAM芯片,A/D 芯片。另一块FPGA 芯片EP2C8F144I8 负责与外部通信,连接了USB 接口芯片,I2C通信芯片和CAN总线通信芯片。

TMS320C6722 型DSP的EMIF接口设计初衷是与外部扩展存储器连接,EMIF接口有两种工作方式:SDRAM工作模式与异步工作模式。SDRAM工作模式是专为 SDRAM设计的同步工作模式,EMIF接口能自动给SDRAM进行刷新;异步工作模式是与SRAM、FLASH等异步器件工作时采用的模式。在本系

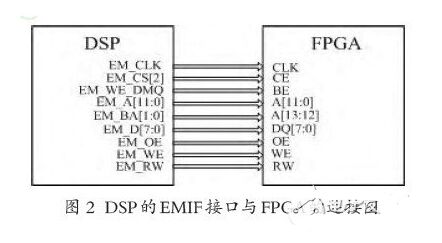

图2 所示是DSP 与一片FPGA 的接口连接图,DSP 与多片FPGA连接时,接口可以按图的方式复用,TMS320C6722 型DSP的EMIF 接口有14 根地址线,与不同FPGA进行通信时,要使用不同的地址。

2.2 DSP 与FPGA 通信时序

2.2.1 异步读操作

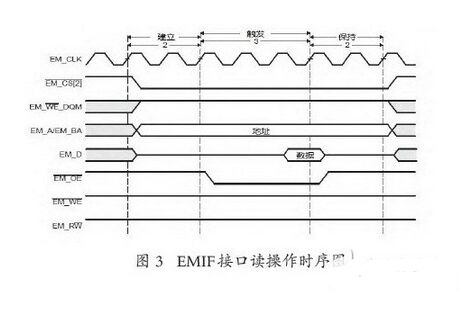

DSP发出对FPGA的读申请时,就会进行异步读操作。当读操作不能在外部器件的一个访问周期内完成时,EMIF就会进行多个周期的操作,直到完成整个申请。

一个EMIF读操作分为建立时间、触发时间和保持时间三部分。在建立时间开始时,EM_CS[2]片选信号拉低,同时地址线EM_A 与EM_BA 给出所读取数据的地址。触发时间开始时,EM_OE信号拉低,同时FPGA在EM_D信号线上传输数据,DSP将在触发时间的最后一个时钟处对数据采样。保持时间中EM_OE 信号将拉高,并在保持时间结束后,EM_CS[2]信号拉高。在整个周期中EM_WE_DQM、EM_WE、EM_RW信号始终为高电平。

2.2.2 异步写操作

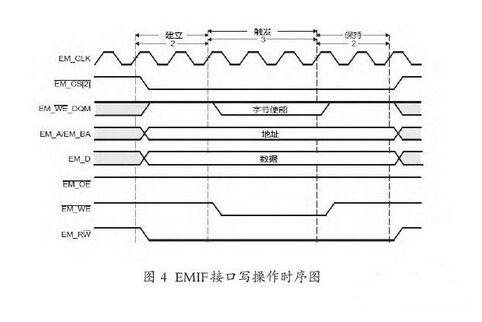

DSP发出对FPGA的写申请时,就会进行异步写操作。当写操作不能在外部器件的一个访问周期内完成时,EMIF就会进行多个周期的操作,直到完成整个申请。

类似于读操作,EMIF 写操作分为建立时间、触发时间和保持时间三部分。在建立时间开始时,EM_CS[2]片选信号拉低,EM_RW信号拉低,同时地址线EM_A与EM_BA 给出所读取数据的地址,数据线EM_D 给出需要写入FPGA的数据。触发时间开始时,EM_WE信号拉低,EM_WE_DMQ信号给出字节使能信号。保持时间开始时EM_WE_DMQ信号与 EM_WE信号拉高,并在保持时间结束后,EM_CS[2]信号与EM_RW信号拉高。在整个写操作周期中EM_OE信号始终为高电平。

DSP 通过配置EMIF 接口的寄存器来实现上述时序,FPGA可采用IP 核来实现EMIF协议,不同的FPGA芯片要采用不同的地址。

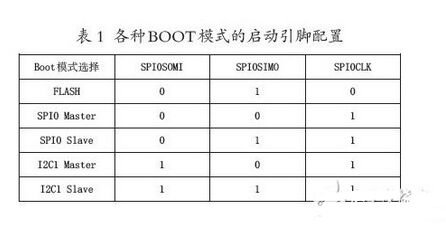

3 系统BOOT 方法

TMS320C6722 型DSP的内部没有可写的ROM,DSP的程序必须存放在外部器件中,DSP 芯片上电后必须首先从外部芯片下载程序。本款DSP可以通过SPI 总线启动、通过I2C总线启动和通过EMIF接口启动。这几种Boot 方式和对应的引脚配置如表1 所示,在本系统中,EMIF接口除了实现通常的数据交换,还兼任带动DSP启动的功能。

系统上电后,DSP 的RESET 引脚要通过下拉电阻拉低,使DSP 处于复位态。FPGA 芯片EP2C8F256I8 上电后从FPGA 配置芯片EPCS4 中下载程序启动。FPGA启动成功后将DSP芯片的SPI0SOMI 引脚与SPI0CLK 引脚拉低,将SPI0SIMO 引脚拉高,然后再将RESET引脚拉高。这样配置是为了使DSP退出复位态时能根据上述3 个引脚的电平获知DSP 芯片将通过EMIF接口启动。此后,DSP芯片将从EMIF 接口读取1KB数据,并将这1KB数据存放于DSP的RAM中,再执行这1KB的程序。

上述过程称为DSP的第一次启动过程。这1KB的程序是由汇编语言编写并通过CCStudio 软件编译成机器语言,存放于FPGA中(通过mif 文件编译进FPGA的程序)。该1KB程序的功能是再次调用EMIF 接口,操作FPGA,使得FPGA 通过IP 核从FLASH芯片中将其余的程序(本系统的程序约为32K)拷入DSP的RAM 中并执行这些新拷入的程序。这是DSP 的第二次启动。第一次启动是硬件启动,是TMS320C6722 型DSP已经设定好的启动方式,第二次启动是软件启动,所执行的启动程序由用户编写。

评论