详解嵌入式流媒体携带式系统的设计及改进

1 引言

本文引用地址:http://www.amcfsurvey.com/article/201807/384682.htm进入20世纪90年代以来,计算机多媒体技术和网络技术飞速发展,基于流媒体的多媒体应用也被运用在多种领域,特别是在图像监控系统和视频点播系统中。目前在便携式流媒体系统发展领域上,竞争的公司主要有三个:Microsoft、Real Networks、Apple,而相应的产品就是:Windows Media、Real Media、QuickTime[2]。本文提出设计的系统优点在于:使用高速低功耗的32位Intel PXA270嵌入式处理器,成本低,稳定性好,实时性好等特点,并对PXA270处理器的接口进行了改进,使系统支持PCI总线协议,具有很好的系统移植性。

2 系统总体结构

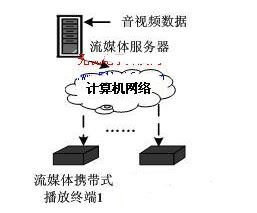

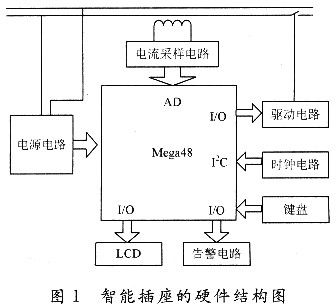

基于高速低功耗的32位RISC嵌入式处理器的流媒体携带式系统如图1所示。

图1 携带式流媒体系统总体结构图

该系统有多个流媒体播放终端,这些播放终端通过无线接入点与计算机网络连接;流媒体服务器通过其以太网接口与计算机网络连接。流媒体服务器可以将从网络上获得的音视频数据转换为流格式的文件;携带式播放终端向流媒体服务器发送请求,流媒体服务器响应请求后,播放终端对服务器发送过来的流媒体数据进行解码和播放,完成工作。

3 流媒体系统的硬件设计

3.1系统的硬件结构

流媒体携带式系统以Intel公司的嵌入式处理器PXA270为核心。Intel PXA270处理器是一个高性能、低价格、低功耗的32位ARM* V.5TE RISC处理器,它集成了I2S,SSP,AC97 等一系列多媒体处理模块,非常适用于多媒体处理、手持设备、PDA等应用领域,是Intel Xscale 系列的第三代的实现。它有一个改进的LCD控制器,一个可扩展的插件接口,摄像采集接口,一个Intel核处理器以及更具保护性的电源管理功能部件等。这个核处理器通过添加MMX和SSE功能单元和附加的音视频处理操作来扩展Intel Xscale微型结构的功能[4]。GEC2410开发板套件

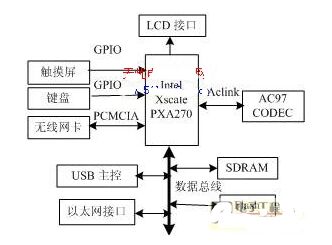

该系统的播放终端需要运行嵌入式操作系统,接收从无线以太网(WLAN)传输过来的音视频数据流,对音视频数据流进行MPEG4解码,输出视频数据和AC97格式的音频数据,并集成触摸屏/键盘输入、USB主控、实时时钟等功能。其硬件结构如图2所示。

图2 流媒体系统的硬件结构图

3.2 PCI接口设计

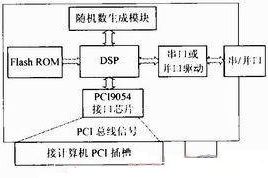

在该流媒体系统设计过程中所使用的PXA270处理器本身并不支持PCI总线协议,为了使系统能够支持PCI总线协议,需要对处理器的接口进行改进,在这里提出使用FPGA来设计PCI总线接口控制器。设计在ModelSim环境下对Verilog HDL源程序进行前仿真,在Xilinx ISE环境下进行逻辑综合、布局布线后下载到Xilinx公司生产Spartan-3 FPGA XC3S200芯片内。GEC2410开发板套件

PCI接口控制器的设计中,核心设计部分有时序控制和配置空间两部分。时序控制保证了PCI接口控制器能按正常的PCI时序工作。配置空间部分保证了板卡的即插即用功能。

3.2.1 PCI接口配置空间的实现

PCI总线定义了3种物理地址空间,分别是存储器地址空间、I/O地址空间和配置地址空间。配置空间是PCI所特有的一种空间,其长度为256字节并且有特定记录结构的地址空间,可以在系统自举时访问,也可在其他时间访问[3]。其它一些寄存器配置如下:GEC2410开发板套件

厂商ID使用芯片最初的生产厂商ID值;设备ID可为除00000000H和0FFFFFFFFH中的任意值;命令寄存器中位1、6、8在本设计中均被设置为0;基地址寄存器用来映射设备的存储器地址空间,与设备地址空间大小相应的低位被强制为0,故此在配置写过程中,配置软件通过对这个寄存器的所有位写1,然后再读出该寄存器的值来决定设备存储器所占用的地址范围,位0被设为低表示存储器映射;类代码寄存器:设置为018000H,即设备为大容量存储控制器;首部类型寄存器:设置为0,表示其为单功能设备且首部类型为0。

3.2.2 时序控制的实现

在时序控制程序中采用状态机模型来实现不同时序的转换。各种命令,数据交换、控制均在状态机的管理下进行工作。PCI总线上的信号是并行工作的,因此,对应每个状态必须明确其执行的任务,这些任务用Verilog语言的进程语句来描述所发生的事件。GEC2410开发板套件

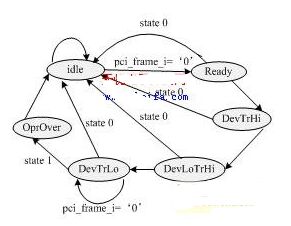

本设计中的状态机共使用了6种状态,如图3所示,分别为空闲状态(idle),准备状态(Ready),DEVSEL# 和TRDY#均为高电平状态(DevTrHi),DEVSEL#为低电平且TRDY#为高电平状态(DevLoTrHi),DEVSEL#和TRDY#均为低电平状态(DevTrLo)以及操作结束状态(OprOver)。

图3 PCI接口状态机

注: state0表示pci_frame_i= ’1’ and pci_irdy_i =’1’, state 1表示pci_frame_i= ’1’ and pci_irdy_i=’0’ and irdy_i=’0’。

当系统接到复位信号后对系统进行复位,然后转入空闲状态。在空闲状态中采样总线,并根据总线的变化来决定下一个时钟上升沿后状态机转人何种状态,这些时序和程序中用到的信号都是基本且必须的,在进行开发时可以根据需要增添必要的状态和信号。编写完整的代码,之后将代码导入ModelSim完成仿真,用Xilinx公司自带工具ISE进行综合布线,生成bit文件下载到FPGA器件。GEC2410开发板套件

4 系统的软件模块设计

该流媒体携带式系统的软件平台采用小体积、高性能的嵌入式Linux操作系统,它由一个内核和一些可以定制的系统模块组成,如文件系统模块、内存驱动模块等[5]。针对本应用,进行了重新剪裁和配置,只包含系统所需的模块。

对于该携带式系统的播放终端,其软件应用程序结构如图4所示,分别是图形用户界面模块、系统管理主控模块和音视频解码器三部分。音视频解码器模块可看作是系统管理主控模块的插件(plug-in),从主控模块获得编码的音视频数据并对其解码,解码后返发送给系统管理主控模块。本文主要介绍系统管理主控模块。

评论