基于J750测试机的S698PM测试程序调试

S698PM芯片是一款抗辐照型的高性能、高可靠、高集成度、低功耗的多核并行处理器SoC芯片,其芯片内部集成了丰富的片上外设,可广泛应用在航空航天、大容量数据处理、工业控制、船舶、测控等应用领域;而J750是业界比较认可测试结果的SOC芯片ATE(Automatic Test Equipment)测试机,市场占有率非常高。下面主要介绍在J750上开发S698PM芯片BSD测试程序及注意事项。

本文引用地址:http://www.amcfsurvey.com/article/201807/384060.htm1.概述

随着SOC芯片系统功能越来越复杂,在一颗芯片中,通常包括有数字部分、模拟部分以及相关的存储器件,甚至有的还有射频模块,这不但对ATE测试设备提出更快、更高的要求,而且还要考虑测试时间成本,因此通常客户会要求测试程序前两项测试项目要能够快速判断出SOC芯片90%常见问题的缺陷。经过多年SOC测试方法和测试原理摸索,逐渐形成前两项测试内容标准:一个是电流功耗测试,另外一个就是BSD测试项目流程。

2.S698PM芯片简介

S698PM芯片是一款抗辐照型的高性能、高可靠、高集成度、低功耗的多核并行处理器SoC芯片; S698PM芯片内部集成了丰富的片上外设,包括常见USB2.0主控器、I2C主控器、以太网控制器等功能模块; S698PM芯片支持RTEMS、 eCOS、VxWorks、Linux等实时嵌入式操作系统,用户可方便地实现嵌入式实时控制系统的高性能多核并行处理设计。

S698PM芯片采用了TMR技术对芯片内部所有逻辑单元进行了三模冗余加固,采用EDAC技术对内部与外部存储器进行了检错纠错加固,因此该芯片的具有很高的抗辐照能力。

S698PM是全球第一款量产化的对标LEON4内核版本的嵌入式SPARC V8多核SOC芯片,其在功能及性能等方面均领先了业界的同类型产品。S698PM代表了当今SPARC嵌入式SOC芯片的最高水平。

3.BSD测试项目原理

BSD(Boundary-scan Diagnostics)的测试原理主要是利用芯片里JTAG电路进行芯片管脚电路检测是否有功能缺陷的测试方法。因此SOC芯片里的JTAG电路主要具备两个功能,并且可通过模式选择管脚来设定。一个功能是通过JTAG电路进行软件配置和调试SOC芯片内核工作参数,实现软件在线调试功能;另一个功能就是通过JTAG口灌入扫描控制信号进行芯片硬件电路的BSD测试或是MBIST测试。

在芯片设计阶段,当插入JTAG电路的同时,会在芯片的所有管脚接口上插入一个带时钟的触发器,并把该时钟信号连接到JTAT_CLK信号上,同时把触发器的输入端和输出端按照扫描链的串行互联方式连接,并把最初的输入端连接到JTAT_DI端,把最后的输出端连接到JTAT_DO端,形成一个闭环的测试链。最后利用工具生成BSD测试程序需要的PATTERN文件,提供给测试机测试需要。

4.基于J750的BSD测试方法

首先,BSD测试需要准备测试向量文件,该文件是由IC设计工程师在插入JTAG电路时,生成的边界扫描向量表文件,同时生成测试机所需的TimingSet参数设置文件,这两个文件共同决定了信号的类型及信号随时钟周期的变化。

信号的常见类型有RH、RL、NR、ROFF、SBC、SBH、SBL等,一般时钟信号的类型为SBL,这样时钟的周期可设、脉冲宽度可控,方便测试机控制该关键信号;其他信号类型一般为NR,方便J750测试机监测。

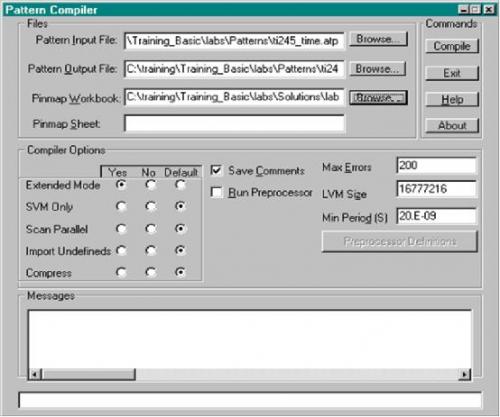

第二步骤,利用J750测试软件Patter Compiler功能模块,把标准PATTERN文件转化成J750识别的格式文件,如下图1所示:

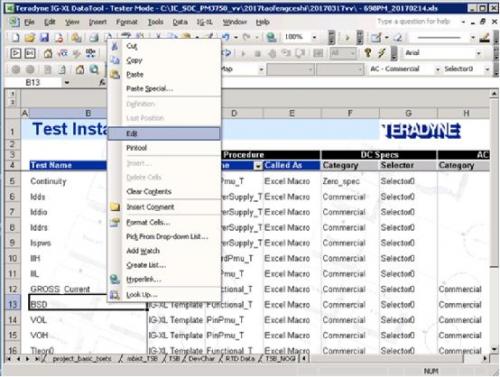

第三步骤,利用J750的测试程序导入功能,将上述两个文件导入到程序里,完成测试机的TimingSet参数等参数设定, 并根据测试机特性及S698PM时序要求可以微调参数,如下图2所示:

第四步骤,设定BSD Function Test功能模块参数,调用BSD测试程序所需的直流和交流参数,以及PATTERN文件。如下图3所示:

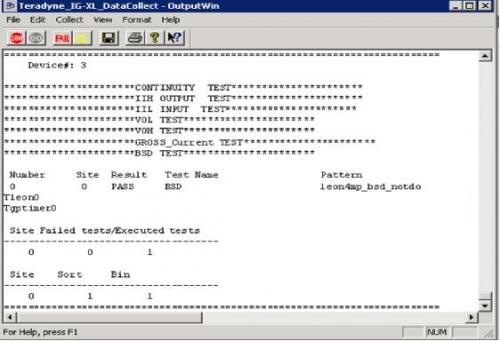

第五步骤,执行BSD function Test命令,在测试过程中,如果结果不满足要求,可进行TimingSet表格中的时间参数微调,测试结果报告如下图4所示:

5.结束语

本文简要介绍了采用 Teradyne-J750EX 自动测试设备来测试嵌入式SoC 芯片S698PM 的BSD测试原理及注意事项。从测试效果来看,因BSD测试方法与芯片内部电路没有太大关系,可以快速判读出芯片管脚电路是否有缺陷,大大地缩短测试时间,从而节省了测试时间,降低了测试成本,因此该BSD测试方法值得推广。

评论