详解半导体分立器件脉冲测试的必要性及相关要求

本文主要讨论了半导体分立器件参数的脉冲测试技术,在这里我们能了解 脉冲测试的必要性是什么,它的相关标准又是什么,实现脉冲测试的方法又是什么。

本文引用地址:http://www.amcfsurvey.com/article/201807/383613.htm一、脉冲测试的必要性

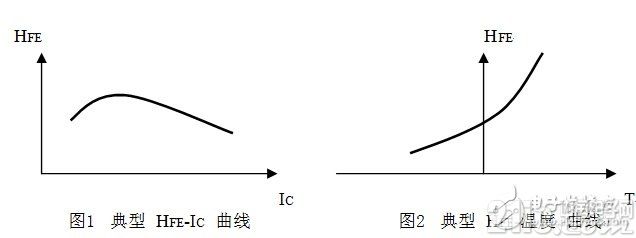

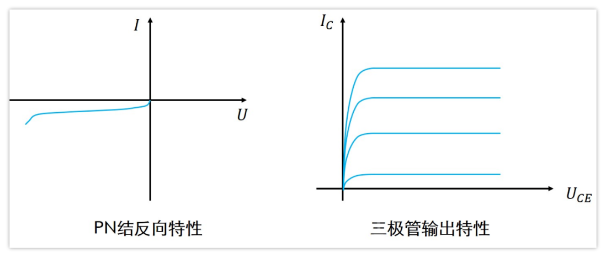

半导体分立器件通常包括二极管、三极管、MOS 埸效应管、结型埸效应管、可控硅、光电耦合器等各种器件。在对这些器件进行参数测试时,需要首先使被测试器件满足参数测试规定的测试条件(即进入规定的工作点),同时也要满足规定的测试环境温度,这样所测的数据才有实际的意义。因为所测试的参数既是测试条件的函数,同时也是环境温度的函数。例如三极管的放大倍数 HFE 既是测试条件 IC 和 VCE 的函数,同时也对环境温度非常敏感。典型 HFE-IC 曲线见图1,典型HFE-温度曲线见图2。

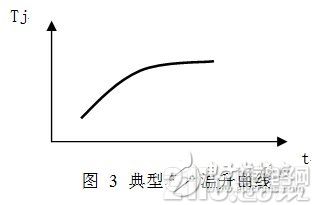

但是除了测试条件和环境温度会影响参数的测试外,有一点容易被人们忽视的是被测器件在测试条件下消耗的功率会对器件的芯片造成附加的温升。附加温升的大小取决于被测器件在规定测试条件下的耗散功率、该功率维持的时间 (即测试时间) 及被测器件的热阻等几方面因素。耗散功率越大、测试时间越长、器件的热阻越大,所造成的芯片附加温升越大。这一点之所以容易被人们忽视是因为们接触的是被测器件的外壳,而很难知道管壳内的芯片到底有多高的温度,这只有通过对器件热阻的测试和研究,才能知道器件芯片的温升曲线是什么样。典型芯片温升曲线见图3。

由于芯片温升曲线的起始段较为陡直,升温速率较快,其附加温升造成的测试数据误差常常比人们想象的严重得多,因为在很多情况下芯片的附加温升不是几度,而是十几度甚至几十度。这时测试环境温度 (尤其是低温测试) 失去了实际的意义。

为了减小附加温升的影响,唯一办法是缩短测试时间。因为参数的测试条件是标准规定的,无法通过改变测试条件来降低器件的功耗,器件的热阻也是客观存在的,只有将测试时间缩短到使芯片附加温升可以忽略不计,这样被测器件的芯片温度才接近规定的测试环境温度。

二、有关标准对脉冲测试的要求

由于器件芯片在参数测试时的附加温升是耗散功率、器件热阻和测试时间的复杂函数,很难用一个简单公式来描述在不同的耗散功率、器件热阻和预期达到的芯片附加温升的情况下,采用多长的测试时间才合理。为了统一测试要求,有关标准规定了脉冲测试的要求和推荐的条件。

1. 美军标准 MIL-STD-750C 半导体器件试验方法 4.3.2.1 规定 :

当在脉冲条件下测量静态及动态参数时,为了避免在测量时由于器件发热引起测量误差,在详细规范中应规定下列条款 :

a. 在测试规定中注明“脉冲测试”。

b. 除非另有规定,脉冲时间 (tp) 为 250-350 微秒,占空比最大为 2%。

2. 国军标 GJB128-86 半导体分立器件试验方法 3.3.2.1 规定 :

为了避免测量时器件发热引起测试误差,要在“脉冲”条件下测试静态和动态参数时,应在详细规范中注明 :

a. 测试中规定应注明“脉冲测试”。

b. 除非另有规定,脉冲宽度应为 250-350μS,占空比为 1-2%。

3. 国标 GB/T 4587-94 (等效 IEC 747-7-1988) 在脉冲法测试的规定条件中指出:

脉冲时间和占空比 (tp,δ), 优先选取 : tp = 300μS, δ≤2%。

4. 国标 GB/T 6218-1996 (等效 IEC 747-7-3:1991) 在对脉冲法测试所作的注释中规定 :

如果采用脉冲法 :

脉冲信号源的脉冲持续时间和占空比 (tp,δ)

优选 : tp = 300μS,δ≤2%。

5. 在晶体管国军标和行军标详细规范 (或空白规范) 中一般对集电极-发射极饱和压降 VCE sat、基极-发射极饱和压降 VBE sat 和正向电流传输比 HFE 规定采用脉冲法。并在脉冲测试的条件的条款中明确规定 :

脉冲测试条件应按 GJB 128 的 3.3.2.1 的规定。

上述标准的有关规定就是通常所说的 300μS 脉冲测试,根据对各种半导体器件的热阻的测试和研究,证明 300μS 脉冲测试的条件是经典的,它可以保证在绝大多数情况下由于测试造成的器件芯片温升可忽略不计。

三、实现脉冲测试的方法

之所以有关标准的详细规范 (或空白规范) 中对 VCE sat、VBE sat 和 HFE 等参数规定采用脉冲法测试,是因为对上述参数进行直流法测试时,器件会承受较大的耗散功率,进而造成器件芯片升温,影响测试数据的真实性,测试时间过长甚至会造成器件的损伤和损坏。

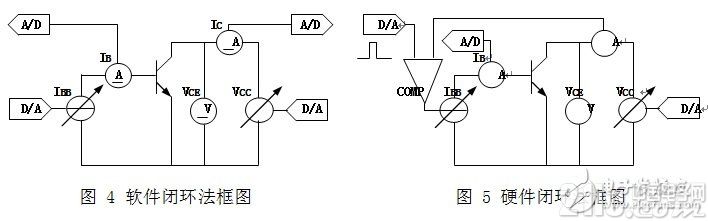

在不同的测试系统中实现脉冲测试 (特别是 HFE 参数的测试) 采用了不同的方法,常见的有软件闭环法 (见图4) 和硬件闭环法 (见图5) 两种。

1. 软件闭环法

软件闭环法测试 HFE 参数的过程如下 :

a. 设置集电极电压源 VCC (可用由 D/A 控制的程控电压源来实现),使 VCE 达到规定的电压值。

b. 设置基极电流源 IB (可用 D/A 控制的程控电流源来实现),读取集电极电流 IC 的值 (可用 A/D 来读取)。

c. 判断集电极电流 IC 的值是否符合测试条件规定的要求 (软件进行判断)。

d. 重复 b 和 c 的过程 (通常采用逐位逼近的方法),使集电极电流 IC 逼近测试条件规定的要求。

e. 读取基极电流 IB 的值 (D/A 的最终设置值),并计算出 HFE 参数的值。

2. 硬件闭环法

硬件闭环法测试 HFE 参数的过程如下 :

a. 设置集电极电压源 VCC (可用由 D/A 控制的程控电压源来实现),使 VCE 达到规定的电压值。

b. 用硬件比较器比较集电极电流 IC 和测试条件规定的 IC 值 (由 D/A 设置),比较的结果控制基极电流源 IBB,进而控制集电极电流 IC 使之自动稳定到规定的 IC 值。

c. 读取基极电流 IB 的值 (A/D 读取),并计算出 HFE 参数的值。

3. 两种测试方法的比较

根据对两种方法测试过程的分析和比较,可以看出存在着如下几方面的差异 :

a. 软件闭环法的控制原理实际上是对直流法人工调节过程的一种改良,从硬件的角度上来讲实际上是一种开环控制。而硬件闭环法是真正采用闭环反馈和自动调节的原理。

b. 软件闭环法由于每次 IB 设置都需要软件介入判别,并需经过多次修改 IB 设置才能使 IC 接近规定的测试工作点,因此整个控制过程时间很长,不可能在 300μS 的时间内稳定测试条件并读取数据,通常需要几毫秒、几十毫秒甚至更长的时间,所以不符合有关标准的规定,同时由于测试时间长导致器件发热,影响了数据的真实性。而硬件闭环法可以在 300μS 时间内实现测试条件的稳定和数据的读取,因而符合有关标准的规定,测试时间造成的器件温升可以忽略不计。

c. 软件闭环法由于从硬件的角度上来讲实际上是一种开环控制,因此集电极电流 IC 只能接近规定值,当被测器件 HFE 数据很大时 (如达林顿管),测试条件会有较大的偏差,进而影响 HFE 数据的精度。而硬件闭环法采用硬件比较和反馈的原理,可以确保测试条件的准确性,对 HFE 有更高的测试精度。

d. 软件闭环法由于实质上是开环控制,从技术上比较容易实现,相对来说不易产生寄生振荡。而硬件闭环法通常由多级放大器与被测器件共同构成闭环反馈系统,处理得不好容易产生寄生振荡。

4. 硬件闭环法的实现

STS 2103A 半导体分立器件测试系统脉冲法测量线路的核心部分是一个高性能的 SM 2204E 模块 (其测试 HFE 参数的简化原理图见图 6 ),该模块用 14 块运算放大器,构成两个功能相同的四相限精密测量单元。每一测量单元都具有恒压、恒流、测压、测流的能力,并支持正、负极性的电压和电流,以适应 NPN 和 PNP 器件的测试。高性能的运算放大器和独特的线路设计使精密测量单元具有良好的频率性能,使之能够满足 300μS 脉冲测试要求,同时还能提供出几十安培的大电流。模块经过精心的调试和补偿,较好地解决了寄生振荡的问题,使系统具有良好的测试适应性,同时还全线实现了开尔文四端法测试,直至被测器件引脚,保证了大电流下的参数测试精度,因而使 STS 2103A 系统体现出良好脉冲测试性能和综合特性。

四、 STS 2103A 半导体分立器件测试系统简介

STS 2103A 半导体分立器件测系统是北京华峰测控技术公司在消化国外系统和调研国内用户的需求和特点的基础上,自行设计开发的智能化两级分布式测试系统,是 STS 2100 系列电子元器件测试系统的重要组成部分,公司拥有该产品的独立知识产权。

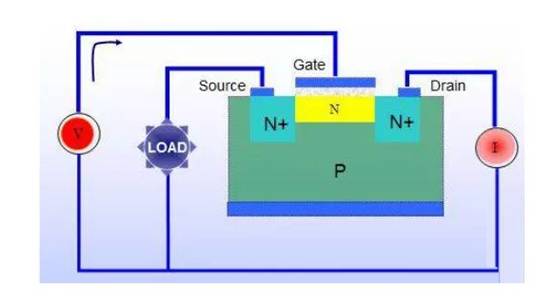

系统主要适用于晶体管三极管 (NPN/PNP)、二极管 (整流、开关、检波、稳压等)、VMOS (N 沟/P 沟)、结型埸效应管、可控硅、光电耦合器及其它各类半导体分立器件。

系统在测试原理和方法上符合国标、国军标和行军标,对集电极-发射极饱和压降 VCE sat、基极-发射极饱和压降 VBE sat 和正向电流传输比 HFE 等参数采用硬件闭环的 300μS 脉冲测试 (脉冲占空比 2%),故可有效抑制测试造成的器件芯片温升,即使在上百瓦功率下进行测试也不会造成器件发热,从而确保测试数据的真实性和稳定性,同时也保证了被测器件的安全。

系统全线采用开尔文电桥四端法进行参数测试,全部测试插座采用美国 3M 公司原装进口四端法测试插座,从而有效扣除了系统及接触环节的接触压降,保证了大电流参数测试的真实性和精度。例如对于三极管饱和压降参数的测试,对于 VMOS 器件导通电阻的测试,对于二极管 (特别是肖特基二极管) 正向压降的测试,即便电流大到几十安培,也具有同样高的测试精度。

系统采用硬件闭环的脉冲工作方式测试 HFE 参数,但同时又具有良好的测试适应性,从低频管到高达几千兆的超高频管,从几十毫瓦的小功率器件到几百瓦的大功率器件,系统都具有良好的测试表现。

系统低压测量单元具有 0.25% 的基本测试精度,这可以保证系统在测量 HFE参数时仍具有优于 1% 的综合精度,符合 GJB 128A-97 中对测量静态参数的误差《 1% 的要求。系统测量 HFE 参数的分辨力达 0.1,并具有良好的稳定性,在测试时用手插拔器件造成器件外壳的微小温升而导致器件 HFE 参数零点几倍的微小变化,系统都能灵敏和稳定地显示出来。

系统在显示测试数据的同时,还具有同屏显示特性曲线的功能,这样在屏幕上不仅可读取精确的测试数据,同时可直观看到器件的击穿特性曲线和输出特性曲线,这对于关心击穿特性曲线形状和输出特性曲线均匀性的用户尤为方便。

系统选用优质元器件和材料,采用数字模拟高压电源技术、测流地线技术、等电位环技术、静电屏蔽技术,软件处理技术,采用悬空架线和三防处理等工艺,使系统具有良好的微弱信号检测能力,即便在潮湿环境下仍可对纳安量级电流进行准确测试。

STS 2103A 半导体分立器件测试系统具有优良的综合性能,是保证半导体分立器件质量的理想检测手段。

评论