基于FPGA的高速光纤通信基带板的设计

作者 袁行猛 徐兰天 中国电子科技集团公司第四十一研究所(安徽 蚌埠 233010)

本文引用地址:http://www.amcfsurvey.com/article/201806/382305.htm*基金项目:中国电科技术创新基金项目《微波毫米波大带宽大规模MIMO测试技术研究》

袁行猛(1988-),男,助理工程师,研究方向:信号与信息处理。

摘要:基于FPGA ( Field Programmable Gate Array)的高速光纤传输系统设计出高速光纤通信基带板。该基带板使用Xilinx公司的Virtex-6系列芯片,使用FPGA中自带的Aurora光口协议的IP核进行例化和设计,并选用了具有高速数据传输通信性能的光模块进行数据传输,实际测试验证了本设计工作可靠性,其功能完善能与更高的控制系统形成灵活对接。该基于FPGA的高速光纤通信基带板是以创新基金项目为依托进行的设计,具体的设计成果能为从事采用FPGA开发光口的高速数据传输方面的工程人员提供较好的实用指导价值。

0 引言

随着现代通信的发展,未来通信无论是有线通还是无线通信对数据的处理能力和数据的传输通信速率的要求都会越来越高,从现在的5G通信的要求中就能明确看到这个要求,所以寻求一种高速、稳定、可靠的通信方式成为现在的主要技术。光纤通信具有传输速度快、损耗低、容量大、占用带宽低、抗电磁干扰的优点,非常适用于高速数据传输[1]。随着现在Xilinx的FPGA芯片的快速发展,处理能力与功能日益增强,本设计选用Xilinx公司的Virtex6系列芯片,设计出具有4通道光口收发,每个通道速率高达6.25 Gb/s的基带板卡,最终此基带板总速率能达到4*6.25 Gb/s。本设计利用这两个部分优势,依附于实际的项目背景设计开发出高速光纤数据传输基带板。最终验证测试本设计的可靠与实用性,满足项目的需求。

1 硬件架构设计

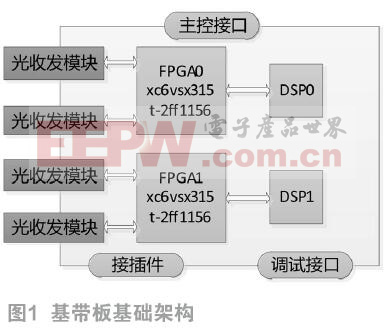

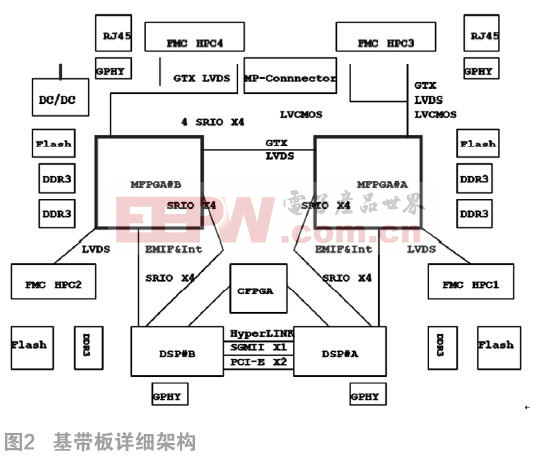

根据本次项目设计需求,本设计的目标是设计出基于FPGA的传输速率高达6.25 Gb/s的光纤数据通信板卡,该板卡上集成高性能FPGA和DSP,板卡能通过预留主控接口实现与上位机之间的通信,并通过DSP进行数据的收发,FPGA与DSP之间的速率通过FIFO进行匹配,最终由FPGA控制光口的通信以及数据的整理功能。由于本设计的速率和处理能力要求高,经过分析仿真,采用2个FPGA和2个DSP的组合处理架构,因此板卡硬件设计采用PCB+FPG(2)+DSP(2)+光模块(4)的架构,并且预留出相应的接插件、主控、调试等接口,设计的基础架构如图1所示,详细设计的架构如图2所示。

在板卡设计中选取的FPGA是Xilinx公司的XC6VSX315T-2FF1156型号作为主控芯片用来控制光纤接口的主要功能,主要完成光收发模块的使能控制、光传输的链路管理以及数据的传输。XC6VSX315T包含49200个Slices和25344 Block RAM,18个用户I/O,可以满足FPGA外围电路设计和后期扩展与增强功能的设计[2]。设计中要求的光口传输速率是6.25 Gb/s,XC6VSX315T共有5组20个GTX数据收发接口,GTX通道的传输速率最快可达6.6 Gb/s,满足技术指标中的信号传输速率的要求[3]。光收发模块选用标准的成熟光收发模块,该模块最高传输速度可达4*6.25 Gb/s。整个板卡选用特定芯片完成主控与基带板之间的数据交互,从而来控制板卡的主要功能。

2 软件架构设计

本次设计基于FPGA的高速光纤通信基带板卡时就采用了Verilog硬件描述语言来作为设计语言,Verilog语言因其容易操作、简单易读、稳定可靠等优越点,在电子自动化设计(EDA)技术的迅猛发展中成为主流语言,也是目前使用最为广泛的硬件描述语言。因此,在本设计中,采用标准的FPGA逻辑设计的基本方式,模块化相应的功能,根据功能进行模块划分,设计中总体分成一个顶层模块和三个子模块。顶层模块主要调用各子模块和设计数据接口,三个子模块为全局时钟管理模块、数据控制与整理模块和Aurora 8B10B IP核的调用模块。本次光口数据传输过程中使用的协议是Xilinx公司提供的一种免费的数据链路层协议——Aurora协议,该协议已经验证是稳定可靠的传输协议,已得到实际应用,该协议核内部封装了高速串行数据接口硬核,可编程逻辑器件通过绑定GTX通道进行数据的收发交互。单个GTX通道的数据传输速率可达G bit级别,根据不同的需求可以实现多个通道的组合使用,从而可实现几十G bit,甚至上百G bit速率的数据传输。因此,本次设计中FPGA逻辑设计的核心模块就采用了Aurora 8B10B IP核。

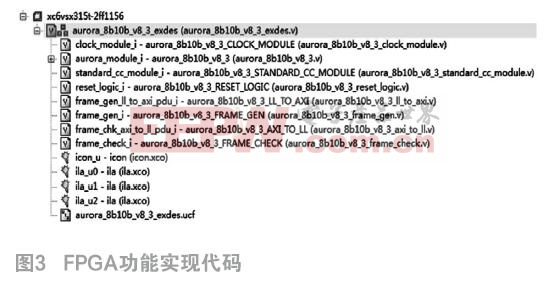

通过例化Aurora 8B10B IP核,生成特定功能需求的模块,数据位宽256位,如图3所示,是主要的FPGA的功能实现代码模块部分。

其中主要实现部分有:顶层模块(aurora_8b10b_v8_3_exdes)、全局时钟管理模块(aurora_8b10b_v8_3_CLOCK_MODULE)、光口通信模块(aurora_8b10b_v8_3)、测试数据控制与产生模块(aurora_8b10b_v8_3_FRAME_GEN)、工程约束文件(aurora_8b10b_v8_3_exdes.ucf)等。

3 光口的IP核协议

3.1 Aurora协议

Aurora协议是由Xilinx公司开发的光纤传输中的串行传输数据的一个链路层协议。它具有高带宽、可扩展性等突出特点已得到实际广泛应用[4]。此外,该协议的帧数据结构也相对简单,数据组包效率较高。因此,它非常适用于点对点的数据传输环境。通常的光口通信链路channel中都会有若干个子lane通道组成,其中每个lane又能实现数据的双工传输。所以本设计中的Aurora协议接口就在Xilinx公司的Virtex-6芯片上实现。

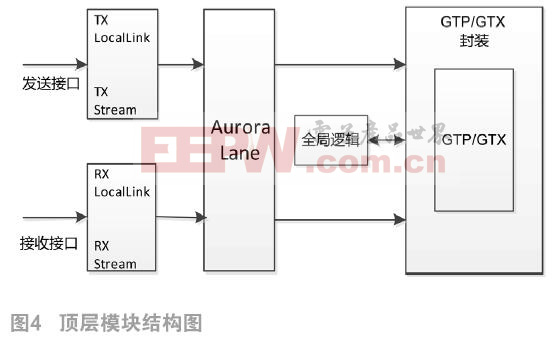

Aurora 8B/10B顶层模块例化了Aurora 8B/10B通道模块、TX和RX本地链路模块、全局逻辑模块以及GTP/GTX收发器。在设计中通过例化IP核会自动生成这些对应模块,具体的顶层模块结构如图4所示。

3.2 8B/10B编解码

8B/10B编码是一种高性能的串行数据编码方式,8B/10B编码的基本特征就是保证编码过程中的DC(直流)平衡,其基本的编码功能就是将8 bit输入数据经过映射编码成10 bit的数据输出,这种编码方式能使数据中“1”和“0”的总个数平衡下来,使其总数最大不超过2,且连续的“1”或“0”的个数不超过5位这样就保证了传输过程中信号的变换频率能保持在一个足够高的水平上。编码的方式是将数据位中的连续8位数据分解成5位和3位的高低两组数据,然后将数据中的低5位信号和高3位的信号分别通过5B/6B编码和3B/4B编码变换成6位和4位信号,然后在合并成一个10 bit的信号输出,以上就是8B/10B编码的基本编码思路。正是因为其具有能让命令信息流频谱分量为0或近乎为0和确保时钟恢复等优点,所以光纤数据传输中采用了8B/10B编码。

编码的作用是提高数据传输的可靠性,因为8B/10B编码的以上优点以及此编码的特性,在光纤通信系统中大都采用8B/10B编码作为主要数据编码方式进行数据传输,从而来保证光纤通信中的数据可靠性,随着技术的发展与实际的应用进展,到目前为止,8B/10B编码也日渐成熟可靠,优点也被充分的利用,也是光口协议中的标准编码形式,本次数据传输中仍采用成熟的8B/10B编码,数据的可靠性能得到充分保障[5]。

4 基带板功能的验证

基带板设计完成后进入基带板测试验证阶段,相应的电路连线完成后,在光口插入相应的光模块,用光纤连接完成后,加载程序,然后用Xilinx自带的观测软件Chipscope观测光口的实际发送与接收到的数据。

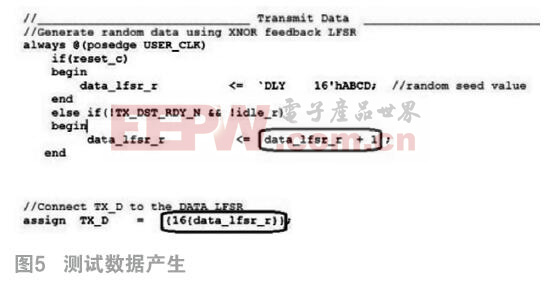

数据端控制为了验证设计的传输的可靠性,手动编写了测试文件,用来传输数据,如图5所示做一个16位累加数(data_lfsr_r),然后数据整理成16*16的256位数据(TX_D),经过光口的发送后,在接收端观测验证。

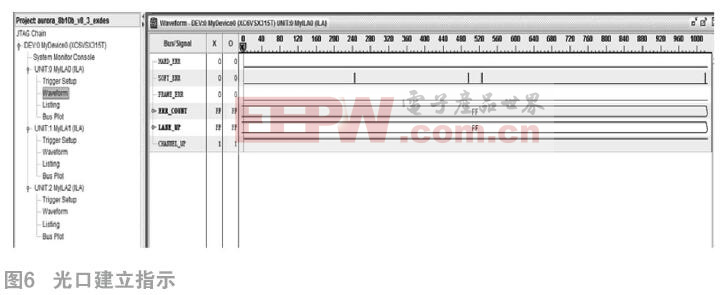

在Chipscope端观测光口链路的建立情况以及数据的收发情况,如图6所示,光口通路的建立情况,图中CHANNEL_UP显示为1,说明链路建立成功,光口正常工作。

随后对光口的发送与接收到数据进行观测,使整个基带板运行起来后,实时观测数据的传输情况,如下图7所示,发送的是256位16进制数(tx_d_i),由于数据位宽较大观测不方便,根据我们的设计思路,设计中的实际位宽是256位,测试中发送的256位数据是由低16位数组合而成,为了观测方便取出低16位数据(tx_d_i[0:15])观测,为了方便比对输入输出数据,编写测试数据,这里设计的是连续发送的由16位累加数数组合而成的256位数据,通过观测比对光口接收数据(rx_d_i)发现,接收到的也是标准累加数,从而验证光口建立成功,数据收发正常,也验证了基带板设计的功能完整性,证实了此次设计的合理与实用性。

设计的基带板中包含两个高性能的Virtex-6 FPGA和两个DSP,FPGA+DSP的联合可以进行数据的高速处理,整套基带板具有完善的数据处理与传输能力,这样就设计出了一整套功能完善的基带板卡。

5 结论

本文设计了一种基于FPGA的高速光纤通信基带板,主要基于光口的高速通信,使用Verilog硬件描述语言设计的一种满足项目需求的基带板,该板卡具有高性能的数据处理能力和高速的传输通信能力,通过实际上板测试,验证了板卡设计的合理性与正确性,满足了实际项目需求,该基带板的设计可以为通信中的高速传输板卡的设计工作者们提供较高的指导意义。

参考文献:

[1]赵梓森.光纤通信的过去、现在和未来[J].光学学报,2011,31(9):99-101.

[2]Xilinx.Virtex-6 Family Overview [Z].America: Xilinx Inc,2015.

[3]Xilinx,Virtex-6 FPGA GTX Transceiver Wizard [Z].America:Xilinx Inc,2018.

[4]候春雷,唐碧华,胡鹤飞,等.基于Aurora的MAC层帧结构的设计与实现[J],中国科技论文在线.2010 (1).

[5]章洁.基于FPGA的高速光纤通信IP核研究设计[J].数字技术与应用,2015,5:29-30.

本文来源于《电子产品世界》2018年第7期第58页,欢迎您写论文时引用,并注明出处。

评论